導入

The Embedded Rust Bookへようこそ。Rustをマイクロコントローラのような、「ベアメタル」の組込みシステムで使うための入門書です。

組込みRustは誰のためのもの

組込みRustは、Rustの高い抽象度と安全性のもと、組込みプログラミングをしたい人のためのものです。 (Rustは誰のためのものも合わせて見て下さい)

スコープ

この本の目的は、以下の通りです。

- 組込みRustをできる限り速く開始できるようにします。すなわち、開発環境のセットアップ方法です。

- 組込み開発におけるRustの現在のベストプラクティスを共有します。つまり、より正しい組込みソフトウェアを書くための、Rustの最善な利用方法です。

- いくつかのケースに対するマニュアルを提供します。例えば、1つのプロジェクト内で、C言語とRustとを混在する方法です。

本書は出来る限り一般的な事項を取り扱います。ただし、説明を簡単にするために、全ての例で、ARM Cortex-Mアーキテクチャを利用します。 読者は、このアーキテクチャに詳しい必要はありません。本書では、アーキテクチャ固有の詳細について、必要に応じて説明をします。

この本は誰のためのもの

本書は、組込み開発か、Rustかのバックグラウンドを持つ人々に向けたものです。しかし、組込みRustに興味がある人なら、誰でも、この本から何かを得られると思います。本書による学習効果を高めるために、事前知識が不足している読者は、「仮定と前提条件」のセクションを読み、不足している知識を補うことをお勧めします。不足知識を補うリソースを見つけるために、「その他のリソース」セクションをチェックすることができます。

仮定と前提条件

- Rustでのプログラミングを楽しんでおり、デスクトップ環境でRustアプリケーションを書いたり、実行したり、デバッグしたりしたことがあることを前提とします。また、本書ではRust 2018を対象とするため、2018 editionのイディオムに慣れ親しんでいる必要があります。

- C, C++, Adaといった言語で組込みシステムを開発、デバッグすることに慣れており、次の概念になじみがあることを想定します。

- クロスコンパイル

- メモリマップ方式のペリフェラル

- 割り込み

- I2C、SPI、シリアルといった一般的なインタフェース

その他のリソース

もしあなたが上述した何らかの事項をよく知らない場合、もしくは、本書内の特定トピックに関して、より詳細な情報を知りたい場合、これらのリソースが役に立つでしょう。

| トピック | リソース | 説明 |

|---|---|---|

| Rust | Rust Book 2018 Edition | もしRustに親しんでいない場合、この本を読むことを強くお勧めします。 |

| Rust、組込み | Embedded Rust Bookshelf | Rust組込みワーキンググループによるいくらかのリソースがあります。 |

| Rust、組込み | Embedonomicon | Rustで組込みプログラミングを行うときのより深い詳細が記載されています。 |

| Rust、組込み | embedded FAQ | 組込みでRustを使う際のよくある質問と回答です。 |

| 割り込み | Interrupt | - |

| メモリマップドI/O/ペリフェラル | Memory-mapped I/O | - |

| SPI, UART, RS232, USB, I2C, TTL | Stack Exchange about SPI, UART, and other interfaces | - |

この本はどう使う

この本は、前から順番に読んでいくことを想定しています。後半の章は、前半の章で説明する概念に基づいて成り立っています。前半の章では、トピックの詳細に深入りせず、後半の章で再訪問します。

この本は、ほとんどの例で、STマイクロエレクトロニクスのSTM32F3DISCOVERY開発ボードを使用します。このボードは、ARM Cortex-Mアーキテクチャをベースとしています。基本機能はこのアーキテクチャベースのCPUでは共通です。一方、ペリフェラルとマイクロコントローラ実装の詳細は、他のベンダーと異なります。同じSTマイクロエレクトロニクスのマイクロコントローラファミリでも、違いがあります。

上記の理由から、本書内の例を理解するために、STM32F3DISCOVERY開発ボードを購入することをお勧めします。

Rustのno_std環境

組込みプログラミングという用語は、様々な分野のプログラミングに使用されます。 たった数キロバイトのRAMかROMが付随する8ビットMCU (例えば、ST72325xx)から、32/64ビットの4コア Cortex-A53 @ 1.4GHzと1GBのRAMが搭載されたRaspberry Pi(Model B 3+)のようなシステムまで、幅広いです。 どのような種類の目的とユースケースがあるか、によって、コードを書くときに異なる制限/限界が課されます。

2つの一般的な組込みプログラミングの分類があります。

ホストされた環境

この分類の環境は、普通のPCの環境に近いです。 これの意味するところは、POSIXのようなシステムインタフェースが提供されている、ということです。システムインタフェースは、ファイルシステムやネットワーク、メモリ管理、スレッドといった多様なシステムとやりとりするための基本要素を提供します。 通常、標準ライブラリは、その機能を実装するために、これらの基本要素に依存します。 また、sysrootや、RAM/ROM利用の制限、そしておそらく特別なハードウェアやIOがあるかもしれません。 全体としては、特殊な用途のPC環境でコーディングをするようなものです。

ベアメタル環境

ベアメタル環境では、高機能なOSが動作していて、私たちのコードをホスティングしてくれる、ということはありません。

これは、基本要素がないことを意味しており、それ故に、デフォルトでは標準ライブラリもありません。

コードにno_stdのマーキングをすることで、そのコードが、ベアメタル環境で実行できることを示します。

no_stdなコードからは、Rustのlibstdとメモリの動的確保が使えません。

しかしながら、no_stdなコードでもlibcoreを使うことができます。libcoreは、ほんの数種類のシンボルを提供することで、いかなる環境でも容易に利用することができます (詳細は、libcoreを参照して下さい)。

libstdランタイム

上述の通り、libstdの利用には、いくらかのシステムインテグレーションが必要です。しかし、これはlibstdがOSの抽象にアクセスするための共通の方法を提供しているだけでなく、ランタイムも提供しているためです。

ランタイムは、とりわけ、スタックオーバーフロープロテクションの準備、コマンドライン引数の処理、メインスレッドの生成、をプログラムのメイン関数が呼び出される前に処理します。

このランタイムも、no_std環境では利用できません。

まとめ

#![no_std]は、クレートレベルの属性で、そのクレートがstdクレートの代わりにcoreクレートとリンクすることを意味します。

libcoreクレートは、プラットフォームに依存しないstdクレートのサブセットです。libcoreクレートは、プログラムが動作するシステムについて前提を置きません。

libcoreクレートは、浮動小数点、文字列やスライスといった言語の基本要素となるAPIと、アトミック操作やSIMD命令といったプロセッサの機能を公開するAPIとを、提供します。一方、プラットフォームインテグレーションを伴うようなAPIは欠如しています。

これらの特性のため、no_stdとlibcoreのコードは、ブートローダー、ファームウェア、カーネルといったあらゆるブートストラップ (ステージ0)のコードにも利用できます。

概略

| 機能 | no_std | std |

|---|---|---|

| ヒープ (動的メモリ) | * | ✓ |

| コレクション (Vec, HashMap, など) | ** | ✓ |

| スタックオーバーフロープロテクション | ✘ | ✓ |

| main関数前の初期化コード実行 | ✘ | ✓ |

| libstdの利用 | ✘ | ✓ |

| libcoreの利用 | ✓ | ✓ |

| ファームウェア、カーネル、ブートローダーのコードを書く | ✓ | ✘ |

* allocクレートを使い、[alloc-cortex-m]のような適切なアロケータを使った場合のみ

** collectionsクレートを使い、グローバルなデフォルトアロケータを設定した場合のみ

参照

ツール

マイクロコントローラを扱う際は、いくつかの異なるツールを利用することになります。あなたのノートPCとは異なるアーキテクチャを扱うことになるでしょうし、リモートデバイス上でプログラムを実行しデバッグする必要があります。

下記リストのツールを利用します。最小バージョンが指定されていない場合、新しいバージョンであれば機能するはずです。私たちがテストしたバージョンをリストに示しています。

- ARM Cortex-Mコンパイルサポートを追加したRust 1.31、1.31-beta以上のツールチェイン。

cargo-binutils~0.1.4qemu-system-arm。テストしたバージョン: 3.0.0- OpenOCD >=0.8.テストしたバージョン: v0.9.0とv0.10.0

- ARMサポートのGDB。バージョン7.12以上を強く推奨。テストしたバージョン: 7.10、7.11、7.12、8.1

- [任意]

gitまたはcargo-generate。どちらもインストールしていないのであれば、どちらをインストールしてもかまいません。

下記に、なぜこれらのツールを利用するのか、を説明します。インストール方法は、次のページにあります。

cargo-generateかgit

ベアメタルプログラムは、非標準 (no_std)なRustプログラムであり、プログラムのメモリレイアウトを正しくするために、リンクプロセスをいじる必要があります。

これには、独特なファイル(リンカスクリプトなど)と設定(リンカフラグ)が必要です。

プロジェクト名やターゲットハードウェアの特徴などを、空白に入力するだけで済むように、テンプレートを用意しています。

このテンプレートは、cargo-generateとの互換性があります。cargo-generateは、テンプレートからCargoプロジェクトを作成するためのCargoのサブコマンドです。

このテンプレートは、gitやcurl、wget、ウェブブラウザを使ってダウンロードできます。

cargo-binutils

cargo-binutilsは、Rustツールチェインとともに配布されているLLVMツールを簡単に使うためのCargoサブコマンド一式です。

これらのツールは、LLVMのobjdumpやnm、sizeを含んでおり、バイナリを調査するために使われます。

GNU binutilsではなく、これらのツールを利用する利点は次の通りです。

(a) LLVMツールのインストールは、OSに関わらず、共通のコマンド1つ(rustup component add llvm-tools-preview)で済みます。

(b) objdumpなどのツールは、rustcがサポートする全てのアーキテクチャ(ARMからx86_64まで)をサポートします。これは、同じLLVMバックエンドを共有しているためです。

qemu-system-arm

QEMUはエミュレータです。今回は、ARMシステムを完全にエミュレートできるものを使います。 私たちは、ホスト上で組込みプログラムを実行するためにQEMUを利用します。 このおかげで、ハードウェアを持っていなくても、この本のいくつかの部分を試すことができます。

GDB

デバッガは、組込み開発で非常に重要です。ホストコンソールにログを記録するような贅沢は、必ずしもできないからです。 場合によっては、ハードウェア上のLEDが点滅しないことがあります。

通常のデバッグ機能に関しては、LLDBはGDBと同様に機能します。しかし、ターゲットハードウェアにプログラムをアップロードするGDBのloadコマンド相当のものは、LLDBにはありません。

したがって、現在はGDBの使用をお勧めします。

OpenOCD

GDBは、STM32F3DISCOVERY開発ボード上のST-Linkデバッグハードウェアと直接通信することはできません。 翻訳プログラムが必要であり、OpenOCD (Open On-Chip Debugger)がその翻訳プログラムです。 OpenOCDは、ノートPCやPC上で動作するプログラムで、GDBのTCP/IPベースのリモートデバッグプロトコルとST-LinkのUSBベースのプロトコルとを翻訳します。

STM32F3DISCOVERY開発ボード上のARM Cortex-Mベースのマイクロコントローラをデバッグするため、OpenOCDは、翻訳の一環として、他の重要な役割も果たします。

- ARM CoreSightデバッグ周辺機器で使用されるメモリマップドレジスタとの通信方法を知っています。CoreSightレジスタは、次のことをできるようにします。

- ブレイクポイント/ウォッチポイント操作

- CPUレジスタの読み込みと書き込み

- CPUがデバッグイベントのために停止したことの検出

- デバッグイベントが発生した後のCPU実行の継続

- 他

- マイクロコントローラのフラッシュの消去と書き込み方法を知っています。

ツールのインストール

このページには、いくつかのツールのOSに依存しないインストール手順を掲載します。

Rustツールチェイン

https://rustup.rsの手順に従って、rustupをインストールします。

注意 コンパイラのバージョンが1.31以上であることを確認して下さい。rustc -vは下記に示す日付より新しい日付を返すべきです。

$ rustc -V

rustc 1.31.1 (b6c32da9b 2018-12-18)

バンド幅とディスク使用量に関する懸念から、デフォルトインストールではネイティブコンパイルのみをサポートします。 ARM Cortex-Mアーキテクチャのクロスコンパイラを追加するために、下記のコンパイルターゲットをインストールします。

$ rustup target add thumbv6m-none-eabi thumbv7m-none-eabi thumbv7em-none-eabi thumbv7em-none-eabihf

cargo-binutils

$ cargo install cargo-binutils

$ rustup component add llvm-tools-preview

OS特有の手順

使用しているOSに特有の手順に従って下さい。

Linux

いくつかのLinuxディストリビューションのインストールコマンドを示します。

Packages

- Ubuntu 18.04以上 / Debian stretch以降

注記 gdb-multiarchは、ARM Cortex-Mプログラムをデバッグするために使用するGDBのコマンドです。

$ sudo apt install \

gdb-multiarch \

openocd \

qemu-system-arm

- Ubuntu 14.04と16.04

注記 arm-none-eabi-gdbは、ARM Cortex-Mプログラムをデバッグするために使用するGDBのコマンドです。

$ sudo apt install \

gdb-arm-none-eabi \

openocd \

qemu-system-arm

- Fedora 27以上

注記 arm-none-eabi-gdbは、ARM Cortex-Mプログラムをデバッグするために使用するGDBのコマンドです。

$ sudo dnf install \

arm-none-eabi-gdb \

openocd \

qemu-system-arm

- Arch Linux

注記 arm-none-eabi-gdbは、ARM Cortex-Mプログラムをデバッグするために使用するGDBのコマンドです。

$ sudo pacman -S \

arm-none-eabi-gdb \

qemu-arch-extra

$ # install openocd from the AUR -- https://aur.archlinux.org/packages/openocd/

udevルール

このルールにより、ルート権限なしで、OpenOCDをDiscoveryボードに対して使えるようにします。

下記の内容で、/etc/udev/rules.dディレクトリにファイルを作成します。

$ cat /etc/udev/rules.d/70-st-link.rules

# STM32F3DISCOVERY rev A/B - ST-LINK/V2

ATTRS{idVendor}=="0483", ATTRS{idProduct}=="3748", TAG+="uaccess"

# STM32F3DISCOVERY rev C+ - ST-LINK/V2-1

ATTRS{idVendor}=="0483", ATTRS{idProduct}=="374b", TAG+="uaccess"

その後、全てのudevルールをリロードします。

$ sudo udevadm control --reload-rules

既にボードをノートPCに接続している場合、一度抜いてから、もう一度接続します。

これらのコマンド実行することで、パーミッションを確認できます。

$ lsusb

(..)

Bus 001 Device 018: ID 0483:374b STMicroelectronics ST-LINK/V2.1

(..)

バス番号とデバイス番号をメモします。それらの番号を、次のコマンドで使用します。

$ # the format of the path is /dev/bus/usb/<bus>/<device>

$ ls -l /dev/bus/usb/001/018

crw-------+ 1 root root 189, 17 Sep 13 12:34 /dev/bus/usb/001/018

$ getfacl /dev/bus/usb/001/018 | grep user

user::rw-

user:you:rw-

パーミッションに追加された+は、パーミッションが拡張されたことを意味しています。

それでは、次のセクションに進んで下さい。

macOS

全てのツールは、Homebrewを使ってインストールできます。

$ # GDB

$ brew tap armmbed/formulae

$ brew install armmbed/formulae/arm-none-eabi-gcc

$ # OpenOCD

$ brew install openocd

$ # QEMU

$ brew install qemu

以上です!次のセクションに進んで下さい。

Windows

arm-none-eabi-gdb

ARMはWindows向けに.exeインストーラを提供しています。hereから1つを入手して、手順に従って下さい。

インストールプロセスが終了する直前に"環境変数にパスを追加"オプションを選択します。

その後、ツールが%PATH%にあることを確認します。

$ arm-none-eabi-gdb -v

GNU gdb (GNU Tools for Arm Embedded Processors 7-2018-q2-update) 8.1.0.20180315-git

(..)

OpenOCD

There's no official binary release of OpenOCD for Windows but there are unofficial releases

available here. Grab the 0.10.x zipfile and extract it somewhere on your drive (I

recommend C:\OpenOCD but with the drive letter that makes sense to you) then update your %PATH%

environment variable to include the following path: C:\OpenOCD\bin (or the path that you used

before).

Windows用のOpenOCDの公式バイナリはありませんが、こちらの非公式なリリースが利用可能です。

0.10.xのzipファイルを入手し、ハードディスクのどこかに展開して下さい(C:\OpenOCDをお勧めしますが、あなたが分かるドライブ名を使用してください)。

その後、%PATH%環境変数がC:\OpenOCD\bin(もしくはあなたがOpenOCDのzipファイルを展開したパス)を含むように更新します。

OpenOCDが%PATH%にあることを確認します。

$ openocd -v

Open On-Chip Debugger 0.10.0

(..)

QEMU

QEMU公式サイトからQEMUを入手します。

ST-LINK USBドライバ

USBドライバもインストールする必要があります。そうでなければOpenOCDは動きません。インストーラの手順に従って下さい。 そして、正しいドライバのバージョン(32ビットか64ビット)をインストールすることを確認して下さい。

以上です!次のセクションに進んで下さい。

インストールの確認

このセクションでは、必要となるツールとドライバが正しくインストールされ、設定されていることを確認します。

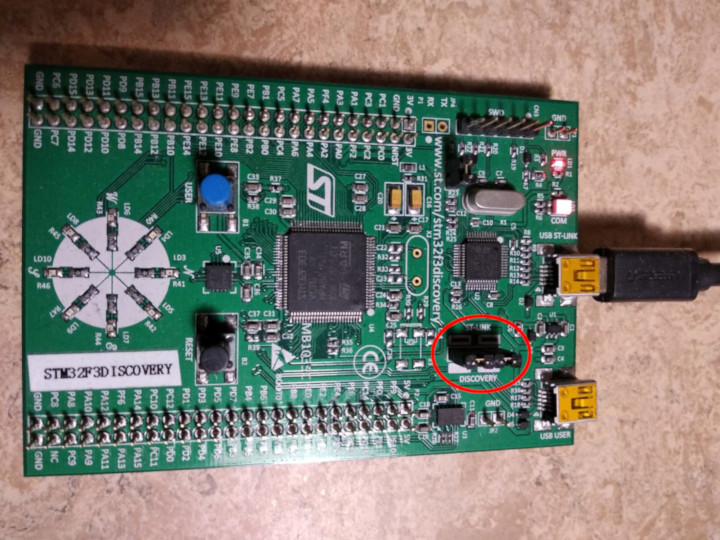

マイクロUSBケーブルを使って、ノートPC / PCをdiscoveryボードに接続して下さい。 discoveryボードは2つのUSBコネクタを搭載しています。 ボード端の中央にある"USB ST-LINK"とラベルが付いたものを使用して下さい。

ST-LINKヘッダが装着されていることも確認します。下の写真の赤丸で囲った部分がST-LINKヘッダです。

それでは、次のコマンドを実行して下さい。

$ openocd -f interface/stlink-v2-1.cfg -f target/stm32f3x.cfg

次の出力が得られ、プログラムはコンソールをブロックするはずです。

Open On-Chip Debugger 0.10.0

Licensed under GNU GPL v2

For bug reports, read

http://openocd.org/doc/doxygen/bugs.html

Info : auto-selecting first available session transport "hla_swd". To override use 'transport select <transport>'.

adapter speed: 1000 kHz

adapter_nsrst_delay: 100

Info : The selected transport took over low-level target control. The results might differ compared to plain JTAG/SWD

none separate

Info : Unable to match requested speed 1000 kHz, using 950 kHz

Info : Unable to match requested speed 1000 kHz, using 950 kHz

Info : clock speed 950 kHz

Info : STLINK v2 JTAG v27 API v2 SWIM v15 VID 0x0483 PID 0x374B

Info : using stlink api v2

Info : Target voltage: 2.919881

Info : stm32f3x.cpu: hardware has 6 breakpoints, 4 watchpoints

確認作業とは直接関係しませんが、ブレイクポイントとウォッチポイントに関する最後の行を取得したはずです。 取得できた場合、OpenOCDプロセスを停止し、次のセクションへ進んで下さい。

"breakpoints"の行が取得できなかった場合、次のコマンドを試してく下さい。

$ openocd -f interface/stlink-v2.cfg -f target/stm32f3x.cfg

このコマンドが機能した場合、古いハードウェアリビジョンのdiscoveryボードを入手したことを意味します。 これは問題になりませんが、後で少し設定を変える必要があるので、そのことを覚えておいて下さい。 次のセクションに進むことができます。

どちらのコマンドも通常ユーザとしてうまく動かなかった場合、rootパーミッションで実行してみて下さい(例えば、sudo openocd ..)。

コマンドがrootパーミッションで機能した場合、udevルールが正しく設定されているか確認して下さい。

ここまで到着していまい、OpenOCDが動いていないならば、issueを作って下さい。私たちがあなたを支援します。

ハードウェアとの出会い

これから作業するハードウェアに詳しくなりましょう。

STM32F3DISCOVERY ("F3")

私たちは、本書内でこのボードを"F3"と呼びます。

このボードには何が搭載されているか見てみましょう。

- STM32F303VCT6マイクロコントローラが1つ。このマイクロコントローラは、次のものを搭載しています。

-

単精度浮動小数点演算をハードウェアサポートし、最大72MHzのクロック周波数で動作するシングルコアのARM Cortex-M4Fプロセッサ

-

256 KiBの"フラッシュ"メモリ (1 KiB = 1024 bytes)

-

48 KiBのRAM

-

多くの"ペリフェラル": タイマ、GPIO、I2C、SPI、USART、他

-

両側面の"ヘッダ"に配置された多数の"ピン"

-

重要 このマイクロコントローラは、約3.3ボルトで動作します。

-

- ジャイロセンサが1つ

- 円形に配置された8個のユーザLED

- 第2のマイクロコントローラ: STM32F103CBT。このマイクロコントローラは、実際には、ST-LINKというオンボードプログラマおよびデバッガの一部であり、"USB ST-LINK"という名前のUSBポートに接続されています。

- "USB USER"というラベルが付いている第2のUSBポート。このUSBポートは、メインマイクロコントローラ (STM32F303VCT6)に接続されており、アプリケーションで利用できます。

入門

このセクションでは、組込みプログラムを書いて、ビルドして、フラッシュに書き込み、デバッグする、という一連のプロセスを説明します。 ほとんどの例を特別なハードウェアなしで試すことができます。有名なオープンソースハードウェアエミュレータであるQEMUを使うからです。 ハードウェアが必要となる唯一のセクションは、当然ながら、OpenOCDを使ってSTM32F3DISCOVERYにプログラムするHardwareセクションです。

QEMU

Cortex-M3マイクロコントローラのLM3S6965用にプログラムを書くところから始めましょう。 このLM3S6965を最初のターゲットとして選んだ理由は、QEMUを使ってエミュレーションできるからです。 このセクションでは、ハードウェアをいじる必要がなく、ツールと開発プロセスに集中できます。

標準ライブラリを使わないRustプログラム

cortex-m-quickstartプロジェクトテンプレートを使用し、新しいプロジェクトを生成します。

cargo-generateを利用する場合

$ cargo generate --git https://github.com/rust-embedded/cortex-m-quickstart

Project Name: app

Creating project called `app`...

Done! New project created /tmp/app

$ cd app

gitを利用する場合

レポジトリをクローンします。

$ git clone https://github.com/rust-embedded/cortex-m-quickstart app

$ cd app

Cargo.tomlのプレースホルダを埋めます。

$ cat Cargo.toml

[package]

authors = ["{{authors}}"] # "{{authors}}" -> "John Smith"

edition = "2018"

name = "{{project-name}}" # "{{project-name}}" -> "awesome-app"

version = "0.1.0"

# ..

[[bin]]

name = "{{project-name}}" # "{{project-name}}" -> "awesome-app"

test = false

bench = false

- どちらも使わない場合

cortex-m-quickstartテンプレートの最新スナップショットを入手し、展開します。

コマンドラインを利用する場合:

$ # 注記 tar形式でも入手可能です: archive/master.tar.gz

$ curl -LO https://github.com/rust-embedded/cortex-m-quickstart/archive/master.zip

$ unzip master.zip

$ mv cortex-m-quickstart-master app

$ cd app

もしくは、cortex-m-quickstartをウェブブラウザで開いて、緑色の「Clone or download」ボタンをクリックして、

「Download ZIP」をクリックします。

次に、Cargo.tomlファイルのプレースホルダを「gitを利用する場合」の2つ目のパートにある通り埋めます。

重要 このチュートリアルでは、「app」という名前をプロジェクト名に使います。 「app」という単語が出てきた場合、それをあなたのプロジェクトにつけた名前に置き替えなければなりません。 または、プロジェクトに「app」という名前をつけると、置き替える必要がなくなります。

これは、src/main.rsのソースコードです。

$ cat src/main.rs

#![no_std] #![no_main] // pick a panicking behavior // パニック発生時の挙動を選びます // extern crate panic_halt; // you can put a breakpoint on `rust_begin_unwind` to catch panics extern crate panic_halt; // パニックをキャッチするため、`rust_begin_unwind`にブレイクポイントを設定できます // extern crate panic_abort; // requires nightly // extern crate panic_abort; // nightlyが必要です // extern crate panic_itm; // logs messages over ITM; requires ITM support // extern crate panic_itm; // ITMを介してメッセージをログ出力します; ITMサポートが必要です // extern crate panic_semihosting; // logs messages to the host stderr; requires a debugger // extern crate panic_semihosting; // ホストの標準エラーにメッセージをログ出力します; デバッガが必要です。 use cortex_m_rt::entry; #[entry] fn main() -> ! { loop { // your code goes here // あなたのコードはここに書きます } }

このプログラムは、標準的なRustプログラムとは少し異なりますので、もう少し詳しく見てみましょう。

#![no_std]はこのプログラムが、標準クレートであるstdにリンクしないことを意味します。

代わりに、そのサブセットであるcoreクレートにリンクします。

#![no_main]は、ほとんどのRustプログラムが使用する標準のmainインタフェースを、

このプログラムでは使用しないことを示します。

no_mainを利用する主な理由は、no_stdの状況でmainインタフェースを使用するにはnightlyが必要だからです。

extern crate panic_halt;。このクレートは、プログラムのパニック発生時の挙動を定義するpanic_handlerを提供します。

後ほど、より詳しく説明します。

[#[entry]]は、cortex-m-rtクレートが提供するアトリビュートで、プログラムのエントリポイントを示すために使用します。

標準のmainインタフェースを使用しないので、プログラムのエントリポイントを示す別の方法が必要です。それが、#[entry]です。

[#[entry]]: https://docs.rs/cortex-m-rt-macros/latest/cortex_m_rt_macros/attr.entry.html

fn main() -> !。ターゲットハードウェア上で動作しているのは私たちのプログラムだけなので、

終了させたくありません。

コンパイル時、確実にそうなるように、発散する関数を使います(関数シグネチャの-> !部分)。

クロスコンパイル

次のステップは、プログラムをCortex-M3アーキテクチャ向けにクロスコンパイルすることです。

これはコンパイルターゲット($TRIPLE)が何かわかっていれば、cargo build --target $TRIPLEを実行するだけで簡単にできます。

コンパイルターゲットが何かは、テンプレート中の.cargo/configを見ればわかります。

$ tail -n6 .cargo/config

[build]

# 以下のコンパイルターゲットから1つを選びます

# target = "thumbv6m-none-eabi" # Cortex-M0およびCortex-M0+

target = "thumbv7m-none-eabi" # Cortex-M3

# target = "thumbv7em-none-eabi" # Cortex-M4およびCortex-M7 (no FPU)

# target = "thumbv7em-none-eabihf" # Cortex-M4FおよびCortex-M7F (with FPU)

Cortex-M3アーキテクチャ向けにクロスコンパイルするためには、thumbv7m-none-eabiを使う必要があります。

このコンパイルターゲットは、デフォルトとして設定されているため、下記2つのコマンドは同じ意味になります。

$ cargo build --target thumbv7m-none-eabi

$ cargo build

確認

今、target/thumbv7m-none-eabi/debug/appに、非ネイティブなバイナリがあります。

cargo-binutilsを使って、このバイナリを確認することができます。

このバイナリがARMバイナリであることを確かめるために、cargo-readobjでELFヘッダを表示できます。

$ # `--bin app`は`target/$TRIPLE/debug/app`のバイナリを確認するためのシンタックスシュガーです

$ # `--bin app`は必要に応じて、バイナリを(再)コンパイルもします

$ cargo readobj --bin app -- -file-headers

ELF Header:

Magic: 7f 45 4c 46 01 01 01 00 00 00 00 00 00 00 00 00

Class: ELF32

Data: 2's complement, little endian

Version: 1 (current)

OS/ABI: UNIX - System V

ABI Version: 0x0

Type: EXEC (Executable file)

Machine: ARM

Version: 0x1

Entry point address: 0x405

Start of program headers: 52 (bytes into file)

Start of section headers: 153204 (bytes into file)

Flags: 0x5000200

Size of this header: 52 (bytes)

Size of program headers: 32 (bytes)

Number of program headers: 2

Size of section headers: 40 (bytes)

Number of section headers: 19

Section header string table index: 18

cargo-sizeはバイナリのリンカセクションのサイズを表示できます。

注記 この出力は、rust-embedded/cortex-m-rt#111がマージされていることを前提とします

$ # 最適化されたバイナリを確認するために`--release`を使います。

$ cargo size --bin app --release -- -A

app :

section size addr

.vector_table 1024 0x0

.text 92 0x400

.rodata 0 0x45c

.data 0 0x20000000

.bss 0 0x20000000

.debug_str 2958 0x0

.debug_loc 19 0x0

.debug_abbrev 567 0x0

.debug_info 4929 0x0

.debug_ranges 40 0x0

.debug_macinfo 1 0x0

.debug_pubnames 2035 0x0

.debug_pubtypes 1892 0x0

.ARM.attributes 46 0x0

.debug_frame 100 0x0

.debug_line 867 0x0

Total 14570

ELFリンカセクションの補足

.textは、プログラムの実行コードを含んでいます.rodataは、文字列のような定数を含んでいます.dataは、初期値が0ではない静的に割り当てられた変数が格納されています.bssも静的に割り当てられた変数が格納されますが、その初期値は0です.vector_tableは、非標準のセクションです。(割り込み)ベクタテーブルを格納するために使用します.ARM.attributesと.debug_*セクションはメタデータを含んでおり、バイナリをフラッシュに書き込む際、 ターゲットボード上にロードされません

重要: ELFファイルは、デバッグ情報といったメタデータを含んでいるため、そのディスク上のサイズは、

プログラムがデバイスに書き込まれた時に専有するスペースを正確に反映していません。

実際のバイナリサイズを確認するために、常にcargo-sizeを使用して下さい。

cargo-objdumpは、バイナリをディスアセンブルするために使用できます。

$ cargo objdump --bin app --release -- -disassemble -no-show-raw-insn -print-imm-hex

注記 この出力は、rust-embedded/cortex-m-rt#111がマージされていることを前提とします

app: file format ELF32-arm-little

Disassembly of section .text:

Reset:

400: bl #0x36

404: movw r0, #0x0

408: movw r1, #0x0

40c: movt r0, #0x2000

410: movt r1, #0x2000

414: bl #0x2c

418: movw r0, #0x0

41c: movw r1, #0x45c

420: movw r2, #0x0

424: movt r0, #0x2000

428: movt r1, #0x0

42c: movt r2, #0x2000

430: bl #0x1c

434: b #-0x4 <Reset+0x34>

HardFault_:

436: b #-0x4 <HardFault_>

UsageFault:

438: b #-0x4 <UsageFault>

__pre_init:

43a: bx lr

HardFault:

43c: mrs r0, msp

440: bl #-0xe

__zero_bss:

444: movs r2, #0x0

446: b #0x0 <__zero_bss+0x6>

448: stm r0!, {r2}

44a: cmp r0, r1

44c: blo #-0x8 <__zero_bss+0x4>

44e: bx lr

__init_data:

450: b #0x2 <__init_data+0x6>

452: ldm r1!, {r3}

454: stm r0!, {r3}

456: cmp r0, r2

458: blo #-0xa <__init_data+0x2>

45a: bx lr

実行

次は、QEMUで組込みプログラムを実行する方法を見ていきましょう。

今回は、実際に何かを行うhelloの例を使います。

便宜上のsrc/main.rsのソースコードです:

$ cat examples/hello.rs

//! Prints "Hello, world!" on the host console using semihosting //! セミホスティングを使って"Hello, world!"をホストのコンソールに表示します #![no_main] #![no_std] extern crate panic_halt; use core::fmt::Write; use cortex_m_rt::entry; use cortex_m_semihosting::{debug, hio}; #[entry] fn main() -> ! { let mut stdout = hio::hstdout().unwrap(); writeln!(stdout, "Hello, world!").unwrap(); // exit QEMU or the debugger section // QEMUもしくはデバッガセッションを終了します debug::exit(debug::EXIT_SUCCESS); loop {} }

このプログラムは、ホストコンソールにテキストを表示するために、セミホスティングと呼ばれるものを使います。 実際のハードウェアを使用する場合、セミホスティングはデバッグセッションを必要としますが、 QEMUを使う場合、これで機能します。

例をコンパイルすることから始めましょう。

$ cargo build --example hello

target/thumbv7m-none-eabi/debug/examples/helloに出力バイナリがあります。

QEMU上でこのバイナリを動かすために、次のコマンドを実行して下さい。

$ qemu-system-arm \

-cpu cortex-m3 \

-machine lm3s6965evb \

-nographic \

-semihosting-config enable=on,target=native \

-kernel target/thumbv7m-none-eabi/debug/examples/hello

Hello, world!

上記コマンドは、テキストを表示したあと、正常終了(終了コードが0)するはずです。 *nixでは、次のコマンドで正常終了したことを確認できます。

$ echo $?

0

この長いQEMUコマンドを分解して説明します。

qemu-system-arm。これはQEMUエミュレータです。QEMUにはいくつかのバイナリがあります。 このバイナリは、ARMマシンのフルシステムをエミュレーションするので、この名前になっています。

-cpu cortex-m3。QEMUに、Cortex-M3 CPUをエミュレーションするように伝えます。 CPUモデルを指定すると、いくつかのコンパイルミスのエラーを検出できます。例えば、 ハードウェアFPUを搭載しているCortex-M4F用にコンパイルしたプログラムを実行すると、 実行中にQEMUがエラーを発生させるでしょう。

-machine lm3s6965evb。QEMUに、LM3S6965EVBをエミュレーションするように伝えます。 LM3S6965EVBは、LM3S6965マイクロコントローラを搭載している評価ボードです。

-nographic。QEMUがGUIを起動しないようにします。

-semihosting-config (..)。QEMUのセミホスティングを有効にします。セミホスティングにより、 エミュレーションされたデバイスは、ホストの標準出力、標準エラー、標準入力を使用できるようになり、 ホスト上にファイルを作成することができます。

-kernel $file。QEMUに、エミュレーションしたマシン上にロードして、実行するバイナリを教えます。

この長いQEMUコマンドを入力するのは大変過ぎます。このプロセスを簡略化するために、

カスタムランナーを設定できます。.cargo/configには、QEMUを起動するランナーが、

コメントアウトされた状態であります。コメントアウトを外して下さい。

$ head -n3 .cargo/config

[target.thumbv7m-none-eabi]

# `cargo run`で、プログラムをQEMUで実行するため、コメントアウトを外して下さい。

runner = "qemu-system-arm -cpu cortex-m3 -machine lm3s6965evb -nographic -semihosting-config enable=on,target=native -kernel"

このランナーは、デフォルトのコンパイルターゲットであるthumbv7m-none-eabiのみに適用されます。

これで、cargo runはプログラムをコンパイルしてQEMUで実行します。

$ cargo run --example hello --release

Compiling app v0.1.0 (file:///tmp/app)

Finished release [optimized + debuginfo] target(s) in 0.26s

Running `qemu-system-arm -cpu cortex-m3 -machine lm3s6965evb -nographic -semihosting-config enable=on,target=native -kernel target/thumbv7m-none-eabi/release/examples/hello`

Hello, world!

デバッグ

デバッグは組込み開発にとって非常に重要です。どのように行うのか、見てみましょう。

組込みデバイスのデバッグは、リモートデバッグを伴います。デバッグしたいプログラムは、 デバッガプログラム(GDBまたはLLDB)を実行しているマシン上で実行されないためです。

リモートデバッグは、クライアントとサーバからなります。QEMUのセットアップで、 クライアントはGDB(またはLLDB)プロセスとなり、サーバは組込みプログラムを実行しているQEMUプロセスとなります。

このセクションでは、コンパイル済みのhelloの例を使用します。

最初のデバッグステップは、QEMUをデバッグモードで起動することです。

$ qemu-system-arm \

-cpu cortex-m3 \

-machine lm3s6965evb \

-nographic \

-semihosting-config enable=on,target=native \

-gdb tcp::3333 \

-S \

-kernel target/thumbv7m-none-eabi/debug/examples/hello

このコマンドは、コンソールに何も表示せず、端末をブロックします。 ここでは2つの追加フラグを渡しています。

-gdb tcp::3333。QEMUがTCPポート3333番で、GDBコネクションを待つようにします。

-S。QEMUが、起動時に、マシンをフリーズします。このフラグがないと、 デバッガを起動する前に、プログラムがmain関数の終わりに到達してしまいます。

次に別の端末でGDBを起動し、helloの例のデバッグシンボルをロードします。

$ <gdb> -q target/thumbv7m-none-eabi/debug/examples/hello

注記: <gdb>はARMバイナリをデバッグ可能なGDBを意味します。

あなたが利用しているシステムに依存して、arm-none-eabi-gdbか、gdb-multiarch、gdbになります。

3つ全てを試してみる必要があるかもしれません。

すると、GDBシェルは、TCPポート3333番で接続を待っていたQEMUに接続します。

(gdb) target remote :3333

Remote debugging using :3333

Reset () at $REGISTRY/cortex-m-rt-0.6.1/src/lib.rs:473

473 pub unsafe extern "C" fn Reset() -> ! {

プロセスは停止しており、プログラムカウンタがResetという名前の関数を指していることがわかります。

Reset関数は、Cortex-Mコアが起動時に実行するリセットハンドラです。

このリセットハンドラは、最終的に、私たちのメイン関数を呼び出します。

ブレイクポイントとcontinueコマンドを使って、メイン関数呼び出しまでスキップしましょう。

(gdb) break main

Breakpoint 1 at 0x400: file examples/panic.rs, line 29.

(gdb) continue

Continuing.

Breakpoint 1, main () at examples/hello.rs:17

17 let mut stdout = hio::hstdout().unwrap();

「Hello, world!」を表示するコードに近づいてきました。

nextコマンドを使って、先へ進みましょう。

(gdb) next

18 writeln!(stdout, "Hello, world!").unwrap();

(gdb) next

20 debug::exit(debug::EXIT_SUCCESS);

この時点で、qemu-system-armを実行している端末に「Hello, world」が表示されるはずです。

$ qemu-system-arm (..)

Hello, world!

もう1度nextを実行すると、QEMUプロセスが終了します。

(gdb) next

[Inferior 1 (Remote target) exited normally]

これでGDBセッションを終了できます。

(gdb) quit

ハードウェア

ここまでで、ツールと開発プロセスにある程度慣れたはずです。このセクションでは、実際のハードウェアに切り替えます。 開発プロセスは、ほとんど同じままです。飛び込みましょう。

ハードウェアを知る

始める前に、プロジェクトの設定に利用するターゲットデバイスのいくつかの特徴を確認する必要があります。

- ARMコア、例えばCortex-M3です。

- そのARMコアはFPUを搭載していますか?Cortex-M4FとCortex-M7Fは、搭載しています。

- ターゲットデバイスに搭載されているフラッシュメモリとRAMの容量はいくらですか? 例えば、フラッシュは256KiBでRAMは32KiBです。

- フラッシュメモリとRAMは、アドレス空間のどこにマッピングされていますか?

例えば、RAMは、通常

0x2000_0000番地に位置します。

これらの情報は、デバイスのデータシートかリファレンスマニュアルに掲載されています。

このセクションでは、私たちのリファレンスハードウェアであるSTM32F3DISCOVERYを使用します。 このボードは、STM32F303VCT6マイクロコントローラを1つ搭載しています。このマイクロコントローラは以下のものを持っています。

- 単精度FPUを含むCortex-M4Fコアが1つ

- 0x0800_0000番地に配置された256KiBのフラッシュメモリ

- 0x2000_0000番地に配置された40KiBのRAM。(別のRAM領域もありますが、説明の簡単化のため、取り扱いません)

設定

テンプレートの新しいインスタンスを使って、スクラッチから書いていきましょう。

cargo-generateを使用しない方法については、前セクションのQEMUを参照して下さい。

$ cargo generate --git https://github.com/rust-embedded/cortex-m-quickstart

Project Name: app

Creating project called `app`...

Done! New project created /tmp/app

$ cd app

第一ステップは、.cargo/configにデフォルトコンパイルターゲットを設定することです。

$ tail -n5 .cargo/config

[build]

# 以下のコンパイルターゲットから1つを選びます

# target = "thumbv6m-none-eabi" # Cortex-M0およびCortex-M0+

# target = "thumbv7m-none-eabi" # Cortex-M3

# target = "thumbv7em-none-eabi" # Cortex-M4およびCortex-M7 (no FPU)

target = "thumbv7em-none-eabihf" # Cortex-M4FおよびCortex-M7F (with FPU)

Cortex-M4Fコアを対象とするものとして、thumbv7em-none-eabihfを使います。

第二ステップは、memory.xファイルにメモリ領域の情報を入力することです。

$ cat memory.x

/* STM32F303VCT6用のリンカスクリプト */

MEMORY

{

/* 注記 1 K = 1 KiBi = 1024バイト */

FLASH : ORIGIN = 0x08000000, LENGTH = 256K

RAM : ORIGIN = 0x20000000, LENGTH = 40K

}

debug::exit()の呼び出しが、コメントアウトされているか削除されていることを確認して下さい。

これは、QEMUで実行する時のみ、使用します。

#[entry] fn main() -> ! { hprintln!("Hello, world!").unwrap(); // exit QEMU // NOTE do not run this on hardware; it can corrupt OpenOCD state // debug::exit(debug::EXIT_SUCCESS); // QEMUを終了する // 注記、ハードウェア上で実行しないで下さい。OpenOCDの状態を破壊する可能性があります。 // debug::exit(debug::EXIT_SUCCESS); loop {} }

これまでやってきた通り、cargo buildでプログラムをクロスコンパイルし、

cargo-binutilsでバイナリを調べることができます。

cortex-m-rtクレートは、チップを動作させるために必要な、全てのおまじないを処理します。

便利なことに、ほとんど全てのCortex-M CPUが同じ方法で起動します。

$ cargo build --example hello

デバッグ

デバッグ方法は少し違います。実際、最初のステップは、ターゲットデバイスによって異なります。 このセクションでは、STM32F3DISCOVERY上で実行しているプログラムをデバッグするために必要となる手順を説明します。 これは、参考の役目を果たします。デバイス固有のデバッグ情報は、 the Debugonomiconを参照して下さい。

以前と同様に、リモートデバッグを行います。クライアントがGDBプロセスであることも同様です。 しかし、今回、サーバはOpenOCDになります。

インストールの確認セクションでやったように、ノートPCまたはPCをdiscoveryボードに接続し、 ST-LINKヘッダが設定されていることを確認して下さい。

discoveryボードのST-LINKに接続するために、端末でopenocdを実行して下さい。

このコマンドは、テンプレートプロジェクトのルートディレクトリから実行して下さい。

openocdは、どのインタフェースファイルとターゲットファイルを使うか、が記述されているopenocd.cfgファイルを見つけます。

$ cat openocd.cfg

# STM32F3DISCOVERY開発ボード用のOpenOCD設定サンプル

# 持っているハードウェアのリビジョンに応じて、これらのインタフェースのうち、1つを選んで下さい。

# 常に、1つのインタフェースがコメントアウトされているべきです。

# Revision C (newer revision)

# リビジョンC (新しいリビジョン)

source [find interface/stlink-v2-1.cfg]

# リビジョンAとB(古いリビジョン)

# source [find interface/stlink-v2.cfg]

source [find target/stm32f3x.cfg]

注記 インストールの確認セクションで、古いバージョンのdiscoveryボードを持っていることが判明している場合、

interface/stlink-v2.cfgを使うようにopenocd.cfgファイルを修正する必要があります。

$ openocd

Open On-Chip Debugger 0.10.0

Licensed under GNU GPL v2

For bug reports, read

http://openocd.org/doc/doxygen/bugs.html

Info : auto-selecting first available session transport "hla_swd". To override use 'transport select <transport>'.

adapter speed: 1000 kHz

adapter_nsrst_delay: 100

Info : The selected transport took over low-level target control. The results might differ compared to plain JTAG/SWD

none separate

Info : Unable to match requested speed 1000 kHz, using 950 kHz

Info : Unable to match requested speed 1000 kHz, using 950 kHz

Info : clock speed 950 kHz

Info : STLINK v2 JTAG v27 API v2 SWIM v15 VID 0x0483 PID 0x374B

Info : using stlink api v2

Info : Target voltage: 2.913879

Info : stm32f3x.cpu: hardware has 6 breakpoints, 4 watchpoints

別の端末で、GDBを実行します。こちらも、テンプレートプロジェクトのルートディレクトから実行して下さい。

$ <gdb> -q target/thumbv7em-none-eabihf/debug/examples/hello

次に、TCP 3333ポートで接続待ちしているOpenOCDに、GDBを接続します。

(gdb) target remote :3333

Remote debugging using :3333

0x00000000 in ?? ()

それでは、loadコマンドを使って、マイクロコントローラにプログラムを書き込んで下さい。

(gdb) load

Loading section .vector_table, size 0x400 lma 0x8000000

Loading section .text, size 0x1e70 lma 0x8000400

Loading section .rodata, size 0x61c lma 0x8002270

Start address 0x800144e, load size 10380

Transfer rate: 17 KB/sec, 3460 bytes/write.

プログラムがロードされました。このプログラムはセミホスティングを使用します。そこで、 セミホスティングを呼び出して何かを行う前に、OpenOCDにセミホスティングを有効にするように、 指示する必要があります。

(gdb) monitor arm semihosting enable

semihosting is enabled

monitor helpコマンドを実行することで、全てのOpenOCDコマンドを見ることができます。

以前のように、ブレイクポイントとcontinueコマンドを使用することで、mainまでスキップすることができます。

(gdb) break main

Breakpoint 1 at 0x8000d18: file examples/hello.rs, line 15.

(gdb) continue

Continuing.

Note: automatically using hardware breakpoints for read-only addresses.

Breakpoint 1, main () at examples/hello.rs:15

15 let mut stdout = hio::hstdout().unwrap();

nextでプログラムを先に進めると、以前と同じ結果になるはずです。

(gdb) next

16 writeln!(stdout, "Hello, world!").unwrap();

(gdb) next

19 debug::exit(debug::EXIT_SUCCESS);

この時点で、OpenOCDコンソールに、他のものと入り混じって「Hello, world!」と表示されるはずです。

$ openocd

(..)

Info : halted: PC: 0x08000e6c

Hello, world!

Info : halted: PC: 0x08000d62

Info : halted: PC: 0x08000d64

Info : halted: PC: 0x08000d66

Info : halted: PC: 0x08000d6a

Info : halted: PC: 0x08000a0c

Info : halted: PC: 0x08000d70

Info : halted: PC: 0x08000d72

もう一度nextを実行して、プロセッサにdebug::exitを実行させます。

これはブレイクポイントとして動作し、プロセスを停止します。

(gdb) next

Program received signal SIGTRAP, Trace/breakpoint trap.

0x0800141a in __syscall ()

また、OpenOCDコンソールに次のものが表示されます。

$ openocd

(..)

Info : halted: PC: 0x08001188

semihosting: *** application exited ***

Warn : target not halted

Warn : target not halted

target halted due to breakpoint, current mode: Thread

xPSR: 0x21000000 pc: 0x08000d76 msp: 0x20009fc0, semihosting

しかし、マイクロコントローラ上で動作しているプロセスは終了していないため、

continueもしくは同様のコマンドを使って、プログラムを再開することができます。

ここで、quitコマンドを使うことで、GDBを終了できます。

(gdb) quit

デバッグにはもう少しステップが必要なので、これらのステップをopenocd.gdbというGDBスクリプトにまとめました。

$ cat openocd.gdb

target remote :3333

# デマングルされたシンボルを表示します

set print asm-demangle on

# 未処理の例外、ハードフォールト、パニックを検出します

break DefaultHandler

break HardFault

break rust_begin_unwind

monitor arm semihosting enable

load

# プロセスを開始しますが、すぐにプロセッサを停止します

stepi

<gdb> -x openocd.gdb $programを実行することで、GDBはすぐにOpenOCDに接続し、

セミホスティングを有効化し、プログラムをロードした上で、プロセスを開始します。

別の方法として、<gdb> -x openocd.gdbをカスタムランナーにして、cargo runでプログラムをビルドし、

さらにGDBセッションを開始することもできます。このランナーは、.cargo/configに含まれていますが、

コメントアウトされています。

$ head -n10 .cargo/config

[target.thumbv7m-none-eabi]

# ここのコメントアウトを外すと、`cargo run`はQEMUでプログラムを実行します

# runner = "qemu-system-arm -cpu cortex-m3 -machine lm3s6965evb -nographic -semihosting-config enable=on,target=native -kernel"

[target.'cfg(all(target_arch = "arm", target_os = "none"))']

# 3つの選択肢のうち、1つのコメントアウトを外すと、`cargo run`はGDBセッションを開始します。

# どの選択肢を使うか、は対象システムによって異なります。

runner = "arm-none-eabi-gdb -x openocd.gdb"

# runner = "gdb-multiarch -x openocd.gdb"

# runner = "gdb -x openocd.gdb"

$ cargo run --example hello

(..)

Loading section .vector_table, size 0x400 lma 0x8000000

Loading section .text, size 0x1e70 lma 0x8000400

Loading section .rodata, size 0x61c lma 0x8002270

Start address 0x800144e, load size 10380

Transfer rate: 17 KB/sec, 3460 bytes/write.

(gdb)

メモリマップドレジスタ

組込みシステムでは、通常のRustコードを実行し、データをRAM内で移動させるだけではたいしたことはできません。 LEDの点滅やボタンの押下検出、もしくは、バス上のオフチップペリフェラルとの通信など、 システムが情報を入出力するには、ペリフェラルとその「メモリマップドレジスタ」の世界に足を踏み入れる必要があります。

マイクロコントローラのペリフェラルにアクセスするためのコードが、次のいずれかのレベルで、既に書かれています。

- マイクロアーキテクチャクレート。この種のクレートは、マイクロコントローラに搭載されているプロセッサコアで共通となる便利なルーチンを扱っています。 また、特定のプロセッサコアを使用する全てのマイクロコントローラに共通のペリフェラルも取り扱います。 例えば、cortex-mクレートは、割り込みの有効化と無効化を行う関数を提供しています。これは全てのCortex-Mベースマイクロコントローラで同じものです。 cortex-mクレートは、「SysTick」ペリフェラルへのアクセスも提供しています。このペリフェラルは、全てのCortex-Mベースマイクロコントローラに搭載されています。

- ペリフェラルアクセスクレート(PAC)。この種のクレートは、薄いラッパーです。特定の型番のマイクロコントローラに対して定義されている、 様々なメモリマップドレジスタのラッパーを提供します。例えば、テキサスインスツルメンツのTiva-C TM4C123シリーズ向けのtm4c123xクレートや、 STマイクロのSTM32F30xシリーズ向けのstm32f30xクレートです。マイクロコントローラのテクニカルリファレンスマニュアルに記載されている各ペリフェラルの操作手順に従って、 レジスタと直接やり取りします。

- HALクレート。これらのクレートは、特定のプロセッサに対して、よりユーザフレンドリなAPIを提供しています。embedded-halで定義されている共通のトレイトを使って実装されていることが多いです。

例えば、このクレートは、

Serial構造体を提供しているでしょう。そのコンストラクタは、適切なGPIOピンの一式とボーレートを引数に取ります。そして、データを送信するためのwrite_byte関数一式を提供します。 embedded-halに関する詳細は、移植性の章を参照して下さい。

- ボードクレート。これらのクレートは、HALクレートのさらに一歩先を進んでいます。これらは、STM32F3DISCOVERYボード向けのF3のように、 特定の開発キットやボード向けに、様々なペリフェラルとGPIOピンを事前に設定してあります。

最下層から始める

全てのCortex-Mマイクロコントローラで共通のSysTickペリフェラルから見ていきましょう。 cortex-mクレートにはかなり低レベルなAPIがあり、次のように使うことができます。

use cortex_m::peripheral::{syst, Peripherals}; use cortex_m_rt::entry; #[entry] fn main() -> ! { let mut peripherals = Peripherals::take().unwrap(); let mut systick = peripherals.SYST; systick.set_clock_source(syst::SystClkSource::Core); systick.set_reload(1_000); systick.clear_current(); systick.enable_counter(); while !systick.has_wrapped() { // Loop // ループ } loop {} }

SYST構造体の関数は、ARMテクニカルリファレンスマニュアルにおいて、このペリフェラルに定義されている機能と非常によく似ています。

「Xミリ秒遅延」といった具合のAPIはありません。whileループを使って愚直に実装する必要があります。Peripherals::take()を呼び出すまでは、

SYST構造体にアクセスできないことに注意して下さい。これは、プログラム全体で唯一のSYST構造体が存在することを保証する特別な手順です。

詳しくは、ペリフェラルセクションをご覧下さい。

ペリフェラルアクセスクレート(PAC)の使用

全てのCortex−Mに搭載されている基本的なペリフェラルのみに限定するのであれば、組込みソフトウェア開発はあまり進まないでしょう。 どこかの時点で、使用している特定のマイクロコントローラ固有のコードを書く必要があります。今回の例では、テキサスインスツルメンツのTM4C123があるとしましょう。 TM4C123はミドルレンジのマイクロコントローラで、80MHzのCortex-M4と256 KiBのフラッシュメモリが搭載されています。 このチップを利用するために、tm4c123xクレートを取得します。

#![no_std]

#![no_main]

// extern crate panic_halt; // panic handler

extern crate panic_halt; // パニックハンドラ

use cortex_m_rt::entry;

use tm4c123x;

#[entry]

pub fn init() -> (Delay, Leds) {

let cp = cortex_m::Peripherals::take().unwrap();

let p = tm4c123x::Peripherals::take().unwrap();

let pwm = p.PWM0;

pwm.ctl.write(|w| w.globalsync0().clear_bit());

// Mode = 1 => Count up/down mode

// モード1は カウントアップ/ダウンモード

pwm._2_ctl.write(|w| w.enable().set_bit().mode().set_bit());

pwm._2_gena.write(|w| w.actcmpau().zero().actcmpad().one());

// 528 cycles (264 up and down) = 4 loops per video line (2112 cycles)

// 528サイクル(264カウントアップとカウントダウン)は、ビデオラインごとに4ループ(2112サイクル)

pwm._2_load.write(|w| unsafe { w.load().bits(263) });

pwm._2_cmpa.write(|w| unsafe { w.compa().bits(64) });

pwm.enable.write(|w| w.pwm4en().set_bit());

}

先ほどSYSTにアクセスした時と全く同じ方法で、PWM0ペリフェラルにアクセスします。違う点は、tm4c123x::Peripherals::take()を呼ぶことです。

このクレートは、svd2rustを使って自動生成されたものです。レジスタフィールドのアクセス関数は、数値の引数ではなく、クロージャを取ります。

このコードは量が多いように見えますが、Rustコンパイラは一連のチェックを実行し、手書きのアセンブラに近いマシンコードを生成します。

自動生成されたコードが、特定のアクセサ関数への全引数が有効であることを判断できない場合、その関数はunsafeとマークされます。

例えば、SVDがレジスタを32ビットと定義しているが、それらの32ビット値の一部が特別な意味を持つかどうか、記述していない場合です。

上記の例では、bits()関数を使ってloadとcompaサブフィールドを設定する時に、unsafeをマークしています。

読み込み

read()関数は、メーカーのSVDファイルで定義されている通り、レジスタ内の様々なサブフィールドに対して、読み込み専用のアクセスオブジェクトを返します。

特定チップ上にある、特定ペリフェラルの、特定レジスタに対して、固有の返り値R型があり、このR型で使える全ての関数は、tm4c123xドキュメントで見ることができます。

if pwm.ctl.read().globalsync0().is_set() {

// Do a thing

// 処理をする

}

書き込み

write()関数は、単一引数のクロージャを取ります。通常は、この引数をwと呼びます。

この引数は、チップメーカーがSVDファイルで定義している通り、様々なレジスタのサブフィールドへの読み書きアクセスを許可します。

特定チップ上にある、特定ペリフェラルの、特定レジスタに対して、w型で使える全ての関数も、tm4c123xドキュメントで見ることができます。

設定していない全てのサブフィールドは、デフォルト値に設定されます。レジスタの既存の内容は失われます。

pwm.ctl.write(|w| w.globalsync0().clear_bit());

修正

レジスタの特定のサブフィールドだけを変更して、残りのサブフィールドは変更したくない場合、modify関数を使えます。この関数は2引数のクロージャを取ります。

1つは読み込み用で、もう1つは書き込み用です。通常、これらの引数をそれぞれ、rとwと呼びます。

r引数は、レジスタの現在の内容を調べるために使用されます。そして、w引数は、レジスタの内容を修正するために使用されます。

pwm.ctl.modify(|r, w| w.globalsync0().clear_bit());

modify関数は、クロージャの本領を発揮します。C言語では、一時変数に読み込み、正しいビットを修正してから、その値を書き戻す必要があります。

これは、エラーが発生するかなりの余地があることを示しています。

uint32_t temp = pwm0.ctl.read();

temp |= PWM0_CTL_GLOBALSYNC0;

pwm0.ctl.write(temp);

uint32_t temp2 = pwm0.enable.read();

temp2 |= PWM0_ENABLE_PWM4EN;

pwm0.enable.write(temp); // ああ!間違った変数です!

HALクレートの使用

あるチップ用のHALクレートは、典型的には、PACによって公開されている生の構造体に対して、カスタムトレイトを実装することで機能しています。

大抵、このトレイトは、単独のペリフェラルにはconstrain()関数を定義し、複数ピンを利用するGPIOポートのようなものにはsplit()関数を定義します。

この関数は、下層の生のペリフェラル構造体オブジェクトを消費し、より高レベルなAPIを備える新しいオブジェクトを返します。

このAPIは、シリアルポートのnew関数が、Clock構造体オブジェクトの借用を必要とするようなことをするかもしれません。Clock構造体オブジェクトは、

PLLと全てのクロック周波数とを設定する関数呼び出しによってのみ、生成することが可能です。この方法では、最初にクロックレートを設定しないでシリアルポートオブジェクトを作成したり、

シリアルポートオブジェクトがボーレートをクロック数に誤って変換するようなことは、静的に起こり得ません。

一部のクレートでは、各GPIOが取り得る状態のための特別なトレイトを定義することさえあります。このトレイトは、ペリフェラルにピンを渡す前に、

ユーザがピンを正しい状態(例えば、適切なAlternate Functionモードを選択することによって)にすることを求めます。

これらは全て、ランタイムのコストを必要としません。

訳注: Alternate Functionモードは、GPIOピンのモードの1つ

例を見てみましょう。

#![no_std] #![no_main] // extern crate panic_halt; // panic handler extern crate panic_halt; // パニックハンドラ use cortex_m_rt::entry; use tm4c123x_hal as hal; use tm4c123x_hal::prelude::*; use tm4c123x_hal::serial::{NewlineMode, Serial}; use tm4c123x_hal::sysctl; #[entry] fn main() -> ! { let p = hal::Peripherals::take().unwrap(); let cp = hal::CorePeripherals::take().unwrap(); // Wrap up the SYSCTL struct into an object with a higher-layer API // SYSCTL構造体をより高レイヤなAPIオブジェクトでラップします let mut sc = p.SYSCTL.constrain(); // Pick our oscillation settings // オシレータの設定値を選択します sc.clock_setup.oscillator = sysctl::Oscillator::Main( sysctl::CrystalFrequency::_16mhz, sysctl::SystemClock::UsePll(sysctl::PllOutputFrequency::_80_00mhz), ); // Configure the PLL with those settings // PLLをそれらの設定値で設定します let clocks = sc.clock_setup.freeze(); // Wrap up the GPIO_PORTA struct into an object with a higher-layer API. // Note it needs to borrow `sc.power_control` so it can power up the GPIO // peripheral automatically. // GPIO_PORTA構造体をより高レイヤなAPIオブジェクトでラップします。 // GPIOペリフェラルに自動的に電源を入れるために、 // `sc.power_control`の借用が必要なことに留意して下さい。 let mut porta = p.GPIO_PORTA.split(&sc.power_control); // Activate the UART. // UARTを起動します。 let uart = Serial::uart0( p.UART0, // The transmit pin // 送信ピン porta .pa1 .into_af_push_pull::<hal::gpio::AF1>(&mut porta.control), // The receive pin // 受信ピン porta .pa0 .into_af_push_pull::<hal::gpio::AF1>(&mut porta.control), // No RTS or CTS required // RTSとCTSは必要としません (), (), // The baud rate // ボーレート 115200_u32.bps(), // Output handling // 出力制御 NewlineMode::SwapLFtoCRLF, // We need the clock rates to calculate the baud rate divisors // ボーレートの除数を計算するためにクロックレートが必要です &clocks, // We need this to power up the UART peripheral // UARTペリフェラルの電源を入れるために必要です &sc.power_control, ); loop { writeln!(uart, "Hello, World!\r\n").unwrap(); } }

セミホスティング

セミホスティングは、組込みデバイスがホスト上でI/Oを行う仕組みです。主に、ホストのコンソールにログ出力するために使われます。 セミホスティングには、デバッグセッションが必要ですが、他には何も必要としません(追加の配線は不要です)。そのため、非常に便利です。 欠点は、非常に低速であることです。ハードウェアデバッガ(例えば、ST-Link)によっては、書き込み操作が数ミリ秒かかります。

cortex-m-semihostingクレートは、Cortex-Mデバイス上でセミホスティング操作をするためのAPIを提供します。

下のプログラムは、セミホスティングバージョンの「Hello, world!」です。

#![no_main] #![no_std] extern crate panic_halt; use cortex_m_rt::entry; use cortex_m_semihosting::hprintln; #[entry] fn main() -> ! { hprintln!("Hello, world!").unwrap(); loop {} }

このプログラムをハードウェア上で実行すると、OpenOCDのログに、「Hello world!」のメッセージが表示されます。

$ openocd

(..)

Hello, world!

(..)

最初に、GDBからOpenOCDのセミホスティングを有効化する必要があります。

(gdb) monitor arm semihosting enable

semihosting is enabled

QEMUはセミホスティング操作を理解しているため、上のプログラムは、デバッグセッションを開始していないqemu-system-armでも動作します。

セミホスティングサポートを有効化するため、QEMUに-semihosting-configフラグを渡す必要があることに注意して下さい。

これらのフラグは、テンプレートの.cargo/configファイルに既に含まれています。

$ # このプログラムは端末をブロックします

$ cargo run

Running `qemu-system-arm (..)

Hello, world!

exitセミホスティング操作もあり、QEMUプロセスを終了するために使われます。

重要:ハードウェア上でdebug::exitを使用しないで下さい。この関数は、OpenOCDセッションを破壊する可能性があり、

OpenOCDを再起動しない限り、それ以上のプログラムのデバッグができなくなります。

#![no_main] #![no_std] extern crate panic_halt; use cortex_m_rt::entry; use cortex_m_semihosting::debug; #[entry] fn main() -> ! { let roses = "blue"; if roses == "red" { debug::exit(debug::EXIT_SUCCESS); } else { debug::exit(debug::EXIT_FAILURE); } loop {} }

$ cargo run

Running `qemu-system-arm (..)

$ echo $?

1

最後のヒント:パニック時の挙動を、exit(EXIT_FAILURE)に設定することができます。

これで、QEMU上で実行できるno_stdランパステストを書くことができます。

利便性のために、panic-semihostingクレートは、「exit」フィーチャを持っています。

このフィーチャが有効化されていると、ホストの標準エラーにパニックメッセージをログ出力した後、exit(EXIT_FAILURE)を呼び出します。

#![no_main] #![no_std] extern crate panic_semihosting; // features = ["exit"] use cortex_m_rt::entry; use cortex_m_semihosting::debug; #[entry] fn main() -> ! { let roses = "blue"; assert_eq!(roses, "red"); loop {} }

$ cargo run

Running `qemu-system-arm (..)

panicked at 'assertion failed: `(left == right)`

left: `"blue"`,

right: `"red"`', examples/hello.rs:15:5

$ echo $?

1

パニック

パニックはRustのコア部分です。インデックス操作のような言語組込みの操作は、メモリ安全性をランタイム時に検査されます。 範囲外のインデックスにアクセスしようとすると、パニックが発生します。

標準ライブラリでは、パニックは定義された動作です。ユーザがパニック発生時にプログラムをアボートする選択をしない限り、 パニックを起こしたスレッドのスタックを巻き戻します。

しかし、非標準のプログラムでは、パニック時の挙動は、未定義のままです。#[panic_handler]関数を宣言することにより、

挙動を選択することができます。この関数は、プログラムの依存関係グラフに、1回だけ現れる必要があります。

そして、 fn(&PanicInfo) -> !のシグネチャを持つ必要があります。

ここで、PanicInfoは、パニックした位置情報を含む構造体です。

組込みシステムは、ユーザとやり取りするものから、安全性が重要な(クラッシュできない)ものまであります。

そのため、全てのパニック時動作に対応できる唯一のものはありませんが、よく利用される挙動がたくさんあります。

これらの一般的な挙動が、#[panic_handler]関数を定義するクレートにまとめられています。

いくつか、例を挙げます。

panic-abort。パニックが発生すると、アボート命令を実行します。panic-halt。パニックが発生すると、プログラム、または、現在のスレッドは、無限ループに入ることで停止します。panic-itm。パニック発生時のメッセージは、ARM Cortex-M固有のペリフェラルであるITMを使ってログ出力されます。panic-semihosting。パニック発生時のメッセージは、セミホスティングを使ってログ出力されます。

crates.ioでpanic-handlerをキーワードに検索することで、さらにクレートを見つけることができます。

プログラムは、対応するクレートとリンクすることで、これらの挙動の中から1つを選びます。 パニック時の挙動がアプリケーションソースコードの中で単一行で表現されていることは、ドキュメントとして有用なだけでなく、 パニック時の挙動をコンパイル時のプロファイルで変更にする時にも利用できます。 例えば

#![no_main]

#![no_std]

// dev profile: easier to debug panics; can put a breakpoint on `rust_begin_unwind`

// 開発プロファイル:パニックのデバッグを容易にします。`rust_begin_unwind`にブレイクポイントを置くことを可能にします。

#[cfg(debug_assertions)]

extern crate panic_halt;

// release profile: minimize the binary size of the application

// リリースプロファイル:アプリケーションのバイナリサイズを最小化します。

#[cfg(not(debug_assertions))]

extern crate panic_abort;

// ..

この例では、開発プロファイルでビルド(cargo build)した時は、panic-haltクレートとリンクします。

しかし、リリースプロファイルでビルド(cargo build --release)した時は、panic-abortクレートとリンクします。

例

配列の長さを超えてアクセスしようとする例を示します。この操作はパニックを引き起こします。

#![no_main] #![no_std] extern crate panic_semihosting; use cortex_m_rt::entry; #[entry] fn main() -> ! { let xs = [0, 1, 2]; let i = xs.len() + 1; // let _y = xs[i]; // out of bounds access let _y = xs[i]; // 範囲外アクセス loop {} }

この例では、panic-semihostingの挙動を選択しており、パニックメッセージは、

セミホスティングを使ってホストコンソールに出力されます。

$ cargo run

Running `qemu-system-arm -cpu cortex-m3 -machine lm3s6965evb (..)

panicked at 'index out of bounds: the len is 3 but the index is 4', src/main.rs:12:13

挙動をpanic-haltに変更し、その場合にメッセージが出力されないことを確認することができます。

例外

例外と割り込みは、プロセッサが非同期イベントと致命的なエラー(例えば、不正な命令の実行)を扱うためのハードウェアの仕組みです。 例外はプリエンプションを意味し、例外ハンドラを呼び出します。例外ハンドラは、イベントを引き起こした信号に応答して実行されるサブルーチンです。

cortex-m-rtクレートは、例外ハンドラを宣言するために、exceptionアトリビュートを提供しています。

// Exception handler for the SysTick (System Timer) exception

// SysTick(システムタイマ)例外のための例外ハンドラ

#[exception]

fn SysTick() {

// ..

}

exception属性の他は、例外ハンドラは普通の関数のように見えます。しかし、もう1つ違いがあります。

exceptionハンドラはソフトウェアから呼び出すことができません。前述の例では、SysTick();というステートメントは、

コンパイルエラーになります。

この動作は、非常に意図的なものです。

これはexceptionハンドラ内で宣言されたstatic mut変数の利用を安全にする、という機能を提供するためのものです。

#[exception]

fn SysTick() {

static mut COUNT: u32 = 0;

// `COUNT` has type `&mut u32` and it's safe to use

// `COUNT`は`&mut u32`の型をもっており、その利用は安全です

*COUNT += 1;

}

ご存知かもしれませんが、static mut変数を関数内で使うことは、その関数を再入不可能にします。

直接的または間接的に、複数の例外・割り込みハンドラから、もしくは、mainと1つ以上の例外・割り込みハンドラから、

再進入不可能な関数を呼び出すことは、未定義動作です。

安全なRustは、決して未定義動作になりません。そのため、再入不可能な関数は、unsafeとマークされなければなりません。

それでも、exceptionハンドラはstatic mutな変数を安全に使える、と述べました。これが可能なのは、どうしてでしょうか。

exceptionハンドラはソフトウェアから呼び出すことができないため、再入する可能性はありません。だから、安全に使えるのです。

完全な例

SysTick例外を大体1秒毎に発生させるシステムタイマの例を使います。

SysTick例外ハンドラは、呼び出された回数をCOUNT変数に記録し、

セミホスティングを使ってホストコンソールにCOUNTの値を出力します。

注記:この例は、どのCortex-Mデバイスでも実行できます。QEMU上でも実行可能です。

#![deny(unsafe_code)] #![no_main] #![no_std] extern crate panic_halt; use core::fmt::Write; use cortex_m::peripheral::syst::SystClkSource; use cortex_m_rt::{entry, exception}; use cortex_m_semihosting::{ debug, hio::{self, HStdout}, }; #[entry] fn main() -> ! { let p = cortex_m::Peripherals::take().unwrap(); let mut syst = p.SYST; // configures the system timer to trigger a SysTick exception every second // 毎秒SysTick例外を起こすためのシステムタイマを設定します syst.set_clock_source(SystClkSource::Core); // this is configured for the LM3S6965 which has a default CPU clock of 12 MHz // デフォルトのCPUクロックが12MHzのLM3S6965向けの設定です syst.set_reload(12_000_000); syst.enable_counter(); syst.enable_interrupt(); loop {} } #[exception] fn SysTick() { static mut COUNT: u32 = 0; static mut STDOUT: Option<HStdout> = None; *COUNT += 1; // Lazy initialization // 遅延初期化 if STDOUT.is_none() { *STDOUT = hio::hstdout().ok(); } if let Some(hstdout) = STDOUT.as_mut() { write!(hstdout, "{}", *COUNT).ok(); } // IMPORTANT omit this `if` block if running on real hardware or your // debugger will end in an inconsistent state // 重要。実際のハードウェアで実行するときは`if`ブロックを削除して下さい。そうでなければ、 // デバッガが不整合な状態に陥るでしょう。 if *COUNT == 9 { // This will terminate the QEMU process // QEMUプロセスを終了します debug::exit(debug::EXIT_SUCCESS); } }

$ tail -n5 Cargo.toml

[dependencies]

cortex-m = "0.5.7"

cortex-m-rt = "0.6.3"

panic-halt = "0.2.0"

cortex-m-semihosting = "0.3.1"

$ cargo run --release

Running `qemu-system-arm -cpu cortex-m3 -machine lm3s6965evb (..)

123456789

Discoveryボードでこのコードを実行すると、OpenOCDコンソールに出力を確認できるでしょう。 プログラムは、カウントが9に到達しても停止しません。

デフォルト例外ハンドラ

exceptionアトリビュートが実際に行っていることは、特定の例外を処理するデフォルト例外ハンドラのオーバーライドです。

特定の例外について、ハンドラをオーバーライドしない場合、DefaultHandler関数がその例外を処理します。

DefaultHandler関数は下記の通りです。

fn DefaultHandler() {

loop {}

}

この関数は、cortex-m-rtクレートによって提供されており、#[no_mangle]とマークされています。

そのため、「DefaultHandler」にブレイクポイントを設定することができ、未処理の例外を捕捉することができます。

exceptionアトリビュートを使うことで、DefaultHandlerをオーバーライドできます。

#[exception]

fn DefaultHandler(irqn: i16) {

// custom default handler

// カスタムデフォルトハンドラ

}

irqn引数は、どの例外が処理されているかを示します。負の値は、Cortex-Mの例外が処理されていることを意味します。

ゼロまたは正の値は、デバイス固有の例外、すなわち、割り込みが処理されていること、を示しています。

ハードフォールトハンドラ

HardFault例外は、少し特別です。この例外は、プログラムが不正な状態になった場合に発生します。

そのため、このハンドラはリターンすることができず、未定義動作を引き起こす可能性があります。

ランタイムクレートは、デバッグ性を向上するために、ユーザ定義のHardFaultハンドラが呼び出される前に、少し仕事をします。

その結果、HardFaultハンドラは、fn(&ExceptionFrame) -> !のシグネチャを持つ必要があります。

ハンドラの引数は、例外によってスタックにプッシュされたレジスタへのポインタです。

これらのレジスタは、例外が発生した瞬間のプロセッサステートのスナップショットで、ハードフォールトの原因を突き止めるのに便利です。

不正な操作を行う例を示します。存在しないメモリ位置への読み込みです。

注記:このプログラムは、QEMU上ではうまく動きません。つまり、クラッシュしません。

qemu-system-arm -machine lm3s6965evbはメモリの読み込みをチェックしないため、 無効なメモリを読み込むと、幸いにも、0を返します。

#![no_main] #![no_std] extern crate panic_halt; use core::fmt::Write; use core::ptr; use cortex_m_rt::{entry, exception, ExceptionFrame}; use cortex_m_semihosting::hio; #[entry] fn main() -> ! { // read a nonexistent memory location // 存在しないメモリ位置を読み込みます unsafe { ptr::read_volatile(0x3FFF_FFFE as *const u32); } loop {} } #[exception] fn HardFault(ef: &ExceptionFrame) -> ! { if let Ok(mut hstdout) = hio::hstdout() { writeln!(hstdout, "{:#?}", ef).ok(); } loop {} }

HardFaultハンドラは、ExceptionFrameの値を表示します。実行すると、

OpenOCDコンソールに次のような表示が見えるでしょう。

$ openocd

(..)

ExceptionFrame {

r0: 0x3ffffffe,

r1: 0x00f00000,

r2: 0x20000000,

r3: 0x00000000,

r12: 0x00000000,

lr: 0x080008f7,

pc: 0x0800094a,

xpsr: 0x61000000

}

pcの値は、例外発生時のプログラムカウンタの値で、例外を引き起こした命令を指しています。

プログラムのディスアセンブル結果を見ます。

$ cargo objdump --bin app --release -- -d -no-show-raw-insn -print-imm-hex

(..)

ResetTrampoline:

8000942: movw r0, #0xfffe

8000946: movt r0, #0x3fff

800094a: ldr r0, [r0]

800094c: b #-0x4 <ResetTrampoline+0xa>

ロード命令(ldr r0, [r0])が例外を発生させたことがわかります。そして、この時のr0レジスタの値は、

0x3fff_fffeです。この値は、ExceptionFrameのr0フィールドと一致します。

割り込み

割り込みは様々な点で例外と違いますが、その動作と使用方法は、ほとんど同じで、同じ割り込みコントローラによって処理されます。 例外がCortex-Mアーキテクチャで定義されているのに対し、割り込みは、命名と機能との両方において、常にベンダ(もっと言うとチップ)固有の実装です。

割り込みは、高度な使い方をしようとする時に必要とされる様々な柔軟性を考慮に入れています。 本書では、そのような高度な使い方は対象外です。しかし、次の点に留意することをお勧めします。

- 割り込みは、ハンドラの実行順序を決めるプログラム可能な優先度を持ちます。

- 割り込みは、ネストとプリエンプションが可能です。つまり、割り込みハンドラの実行は、より優先度の高い割り込みに割り込まれる場合があります。

- 通常、割り込み要因は、割り込みハンドラが無限に再呼び出しされないようにするため、クリアされる必要があります。

ランタイムでの一般的な初期化手順は、常に同じです。

- 必要な時に割り込み要求を起こすように、ペリフェラルを設定します

- 割り込みコントローラで割り込みハンドラの優先度をセットします

- 割り込みコントローラで割り込みハンドラを有効化します

例外と同様に、例外ハンドラを宣言するために、cortex-m-rtクレートは、interrupt属性を提供しています。

利用可能な割り込み(そして割り込みハンドラテーブルでの配置)は、通常、svd2rustを使ってSVDから自動生成されます。

// Interrupt handler for the Timer2 interrupt

// タイマ2割り込みの割り込みハンドラ

#[interrupt]

fn TIM2() {

// ..

// Clear reason for the generated interrupt request

// 発生した割り込み要求の原因をクリアします

}

割り込みハンドラは、通常の関数のように見え、例外ハンドラに似ています(引数がないことを除いて)。 しかし、割り込みハンドラは、特別な呼び出し規約のため、ファームウェアの他の部分から直接呼び出すことができません。 ソフトウェアで割り込み要求を起こし、割り込みハンドラへの転送を発生させることは可能です。

例外ハンドラと同様に、割り込みハンドラ内でstatic mut変数を宣言し、状態を安全に保持することができます。

#[interrupt]

fn TIM2() {

static mut COUNT: u32 = 0;

// `COUNT` has type `&mut u32` and it's safe to use

// `COUNT`は`&mut u32`の型を持っており、その使用は安全です

*COUNT += 1;

}

ここで示した仕組みの詳細については、例外セクションを参照して下さい。

IO

TODO Cover memory mapped I/O using registers.

ペリフェラル

ペリフェラルとは何か?

ほとんどのマイクロコントローラはCPUやRAM、フラッシュメモリ以外のものを持っています。マイクロコントローラはシリコン上に専用のセクションを持っており、そのセクションは、マイクロコントローラの外のシステムとやり取りしたり、センサーやモーターコントローラ、またはディスプレイもしくはキーボードのようなヒューマンインタフェースによって世界中の周囲環境と直接的または間接的にやり取りするために使用されます。それらのコンポーネントはまとめてペリフェラルと呼ばれています。

これらのペリフェラルは有用です。なぜならば、開発者はペリフェラルに処理をオフロードすることが可能になるため、全ての処理をソフトウェアで行う必要がなくなります。デスクトップ開発者がグラフィック処理をビデオカードにオフロードするのと同じように、組込み開発者は一部のタスクをペリフェラルにオフロードして、CPUの時間を他の重要なことに使ったり、電力を節約するために何もしないようにすることができます。

1970年代か1980年代の旧式の家庭用コンピュータのメイン回路基板を見れば(実際に、旧式のデスクトップPCは今日の組込みシステムとさほど違いません)、次のものを目にするはずです。

- プロセッサ

- RAMチップ

- ROMチップ

- I/Oコントローラ

RAMチップ、ROMチップ、I/Oコントローラ(このシステムのペリフェラル)は「バス」として知られる一連の並列な配線を通してプロセッサに接続されているでしょう。アドレスバスは、プロセッサがバス上のどのデバイスと通信したいかを選択するアドレス情報を運び、データバスは、実際のデータを運びます。組込みマイクロコントローラにおいても、同じ原理が適用されます。それは全てが1つのシリコン片に詰め込まれているということです。

しかしながら、VulkanやMetal、OpenGLなどのソフトウェアのAPIを通常持つグラフィックカードとは異なり、ペリフェラルはメモリチャンクにマッピングされたハードウェアインターフェースとしてマイクロコントローラに公開されています。

線形な実メモリ空間

マイクロコントローラでは、0x4000_0000や0x0000_0000のような任意のアドレスにデータを書き込むことは、完全に正当な行為でしょう。

デスクトップシステムでは、メモリアクセスはMMU(メモリ管理ユニット)によって厳密に制御されています。このコンポーネントは2つの主な役割を持っています。メモリのセクションへのアクセス権限の強制(あるプロセスが別のプロセスのメモリを読み出したり変更したりできないようにする)、そして物理メモリのセグメントをソフトウェアで使用される仮想メモリ範囲に再マッピングすることです。マイクロコントローラは通常はMMUを持たず、代わりにソフトウェアで物理アドレスのみを使用します。

32ビットマイクロコントローラは0x0000_0000から0xFFFF_FFFFの線形な実アドレス空間を持ちますが、それらは大抵の場合、実際のメモリのためにはその範囲の数百キロバイトしか使用しません。これにより、かなりの量のアドレス空間が残ります。前の章では、RAMが0x2000_0000のアドレスに配置されていることについて話しました。もしもRAMが64KiBの長さなら(すなわち、最大アドレスが0xFFFF)、0x2000_0000から0x2000_FFFFがRAMのアドレスに対応します。0x2000_1234のアドレスにある変数に書き込むと、内部ではアドレスの上位部分(この例では0x2000)を検出し、アドレスの下位部分(この例では0x1234)に作用できるようにRAMをアクティブにします。Cortex-Mにおいては、フラッシュROMも0x0000_0000から0x0007_FFFFのアドレスにマッピングされています(512KiBのフラッシュROMが載っている場合)。これら2つの領域の間に残るスペースを全て無視するのではなく、代わりにマイクロコントローラの設計者は特定のメモリ配置にペリフェラルのインターフェースをマッピングしました。これは次のようなものになります。

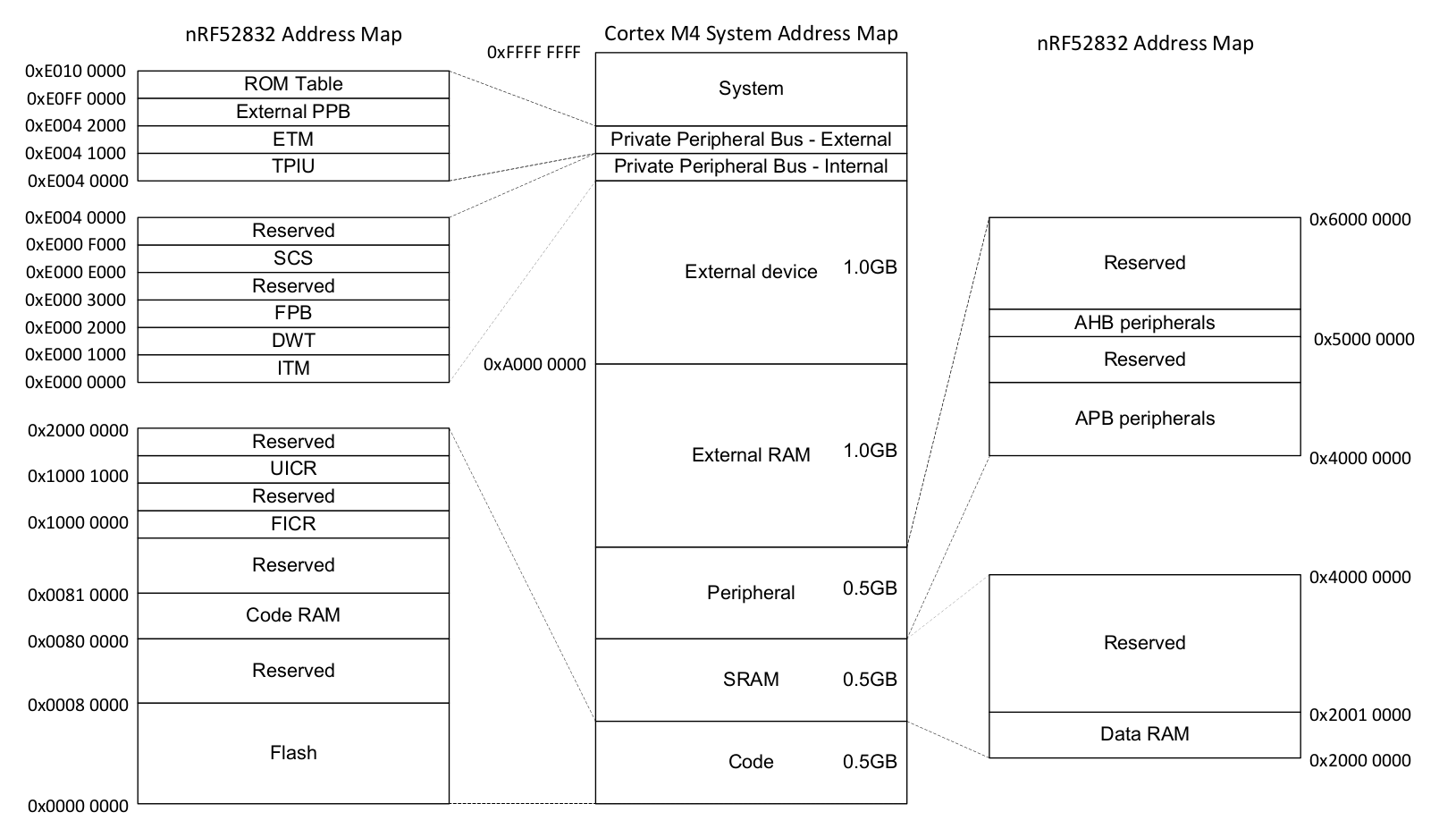

Nordic nRF52832 Datasheet (pdf)

メモリマップド・ペリフェラル

一見すると、これらのペリフェラルとのやり取りは簡単です。正しいデータを正しいアドレスに書き込むだけです。例えば、32ビットワードをシリアルポート上で送信することは、32ビットワードを特定のメモリアドレスに書き込むことと同じくらい直接的になり得ます。シリアルポート・ペリフェラルは自動的にデータを引き受けて送信します。

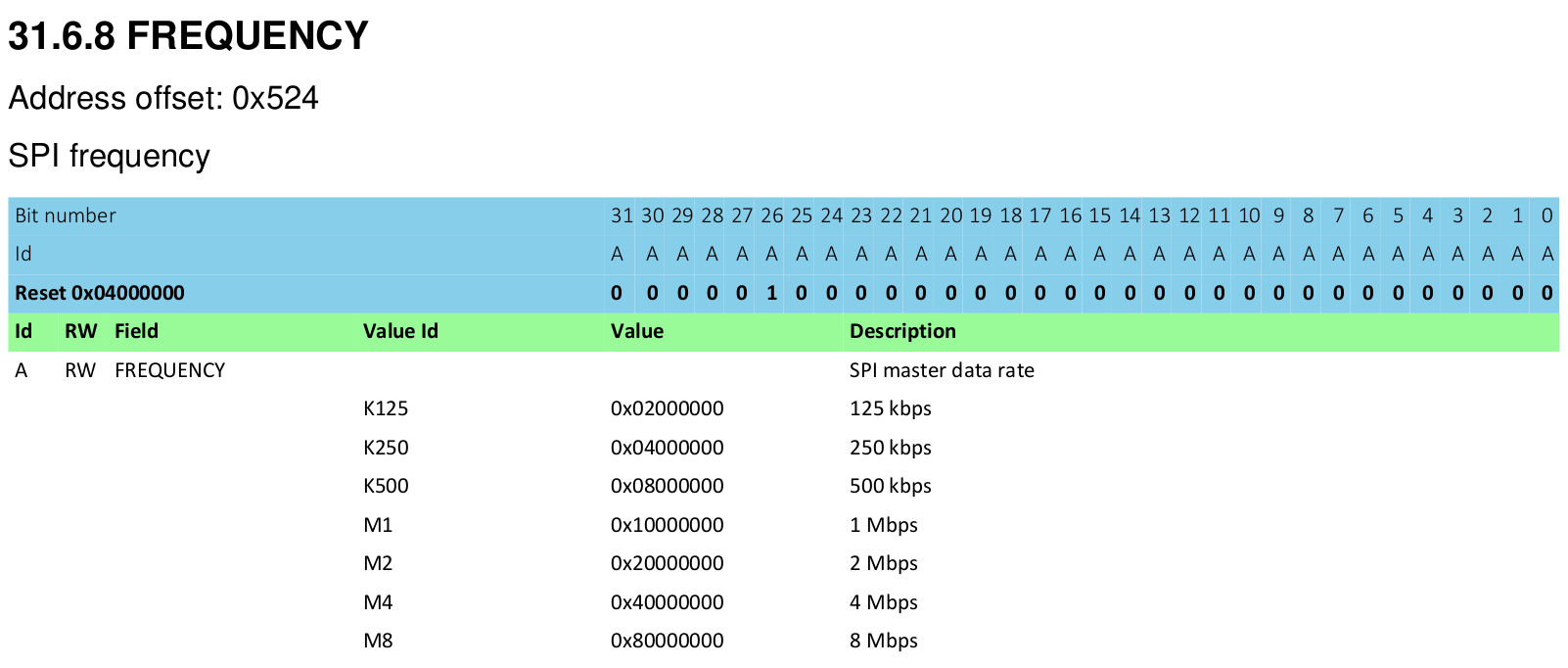

これらのペリフェラルの設定についても同じように動作します。ペリフェラルの設定をするための関数を呼ぶ代わりに、ハードウェアAPIとして機能するメモリチャンクが公開されます。0x8000_0000をSPI周波数の設定レジスタに書き込むと、SPIポートは8Mbpsでデータを送信するようになります。0x0200_0000を同じアドレスに書き込むと、SPIは125Kbpsでデータを送信するようになります。これらの設定レジスタをちょっとだけ見てみます。

Nordic nRF52832 Datasheet (pdf)

アセンブリ言語やC言語、Rustなど、どの言語が使われようとも、このインターフェースがどのように作用するかはハードウェアによって定められています。

最初の試み

レジスタ

SysTick ペリフェラルを見ていきましょう。 SysTick はCortex-Mプロセッサ・コアに搭載されているシンプルなタイマーです。

通常は、チップメーカーのデータシートやテクニカルリファレンスマニュアルでこれらのペリフェラルの情報を調べることができるのですが、この例においては全てのARM Cortex-Mコアで共通のものですので、今回はARMリファレンスマニュアルを見てみましょう。

そこには4つのレジスタが載っています。

| オフセット | 名前 | 説明 | 幅 |

|---|---|---|---|

| 0x00 | SYST_CSR | 制御およびステータスレジスタ | 32ビット |

| 0x04 | SYST_RVR | リロード値レジスタ | 32ビット |

| 0x08 | SYST_CVR | 現在値レジスタ | 32ビット |

| 0x0C | SYST_CALIB | キャリブレーション値レジスタ | 32ビット |

Cアプローチ

Rustでも、structを使ってCと同じ方法でレジスタの集合を正確に表現することができます。

#[repr(C)]

struct SysTick {

pub csr: u32,

pub rvr: u32,

pub cvr: u32,

pub calib: u32,

}

#[repr(C)]修飾子はRustコンパイラ対して、この構造体をCコンパイラと同じようにメモリにレイアウトするように指示します。

これはとても重要なことです。なぜならRustでは、Cにおいては行われない構造体のフィールドの並び替えが許されているためです。

コンパイラによって暗黙のうちに構造体のフィールドが並び替えられることにより、デバッグをするはめになることは想像できるでしょう!

この修飾子を置くことで、4つの32ビットの各フィールドは上記のテーブルに対応付けられます。

ただしもちろん、このstructはそれ自体では何の役にも立ちません。次のように変数として使う必要があります。

let systick = 0xE000_E010 as *mut SysTick;

let time = unsafe { (*systick).cvr };

volatileアクセス

上記のやり方には、いくつか問題があります。

- ペリフェラルにアクセスするためには毎回アンセーフを使わなくてはなりません。

- どのレジスタが読み取り専用でどのレジスタが読み書き可能かを指定する方法がありません。

- プログラム内のどのコードからでもこの構造体を通してハードウェアにアクセスできてしまいます。

- 最も大事なことは、このコードは実際には動作しないということです…

ここで問題となるのは、コンパイラが賢いということです。

同じRAMに相次いで2回書き込むと、コンパイラはこれに気づき、最初の書き込みを完全にスキップします。

Cでは、全ての読み書きが意図した通りに行われることを保証するために、volatile型修飾子を変数につけることができます。

Rustでは、変数ではなくアクセスに対してvolatileをつけます。

let systick = unsafe { &mut *(0xE000_E010 as *mut SysTick) };

let time = unsafe { core::ptr::read_volatile(&mut systick.cvr) };

これで4つの問題のうち1つを直せました。しかし、さらにunafeなコードがあります!

幸いなことに、これに対処できるサードパーティ製のクレートvolatile_registerがあります。

use volatile_register::{RW, RO};

#[repr(C)]

struct SysTick {

pub csr: RW<u32>,

pub rvr: RW<u32>,

pub cvr: RW<u32>,

pub calib: RO<u32>,

}

fn get_systick() -> &'static mut SysTick {

unsafe { &mut *(0xE000_E010 as *mut SysTick) }

}

fn get_time() -> u32 {

let systick = get_systick();

systick.cvr.read()

}

これでreadとwriteメソッドを通してvolatileアクセスが自動的に行われるようになりました。

書き込みを実行するのはまだunsafeです。しかし、公平を期するために言うと、ハードウェアは変更可能な状態の集まりであるため、それらへの書き込みが実際に安全なのかどうか、をコンパイラが知る方法はないのです。そのため、これは基本姿勢としては悪くないでしょう。

Rustのラッパ

ユーザが安全に呼び出せるように、このstructを高レイヤーのAPIでラップする必要があります。

ドライバの作者として、アンセーフなコードが正しいことを手動で検証し、ユーザがそのドライバを使用する上で心配することがないように安全なAPIとして提供します。(ユーザは提供されたものが正しいと信頼しています!)

一例を挙げます。

use volatile_register::{RW, RO};

pub struct SystemTimer {

p: &'static mut RegisterBlock

}

#[repr(C)]

struct RegisterBlock {

pub csr: RW<u32>,

pub rvr: RW<u32>,

pub cvr: RW<u32>,

pub calib: RO<u32>,

}

impl SystemTimer {

pub fn new() -> SystemTimer {

SystemTimer {

p: unsafe { &mut *(0xE000_E010 as *mut RegisterBlock) }

}

}

pub fn get_time(&self) -> u32 {

self.p.cvr.read()

}

pub fn set_reload(&mut self, reload_value: u32) {

unsafe { self.p.rvr.write(reload_value) }

}

}

pub fn example_usage() -> String {

let mut st = SystemTimer::new();

st.set_reload(0x00FF_FFFF);

format!("Time is now 0x{:08x}", st.get_time())

}

このやり方の問題は、次のコードがコンパイラに完全に受け入れられることです。

fn thread1() {

let mut st = SystemTimer::new();

st.set_reload(2000);

}

fn thread2() {

let mut st = SystemTimer::new();

st.set_reload(1000);

}

set_reload関数に&mut self引数を渡すことで、そのインスタンスのSystemTimer構造体に対する他の参照がないことを確認しますが、全く同じペリフェラルを指す2つ目のSystemTimer構造体をユーザが作ることは止められません!

このように書かれたコードは、作者がこれらの「重複した」ドライバのインスタンスを全て見つけるのに十分に熱心であれば動作するでしょうが、一度コードが複数のモジュール、ドライバ、開発者、そして日に渡って分散すると、この種の間違いがどんどん入り込みやすくなっていきます。

ミュータブルでグローバルな状態

残念ながら、ハードウェアは基本的にミュータブルでグローバルな状態に他なりません。これはRustの開発者にとって非常に恐ろしいことです。 ハードウェアは書かれたコードの構造とは独立して存在しており、現実の世界からいつでも変更される可能性があります。

何をルールとするべきか?

どうすればこれらのペリフェラルと確実にやり取りできるのでしょう?

- いつ変化するかわからないペリフェラルメモリの読み書きには、常に

volatileメソッドを使用してください - ソフトウェアでは、これらのペリフェラルへの読み取り専用アクセスをいくつでも共有できるでしょう

- あるソフトウェアがあるペリフェラルに読み書きのアクセスをするならば、そのソフトウェアは、ペリフェラルへの唯一の参照を持つべきです

借用チェッカ

さきほどのルールの最後の2つは、借用チェッカが行っていることに怪しいくらいよく似ています。

ペリフェラルの所有権を譲渡したり、ペリフェラルへのイミュータブルまたはミュータブルな参照を提供したりできるのか、を想像してみてください。

それは可能です。ただし、借用チェッカが正しくペリフェラルの所有権や参照を扱うためには、各ペリフェラルが持つインスタンスはただ1つにする必要があります。そうすれば、Rustはこれを正しく扱えます。 幸いなことにハードウェアにおいて、任意のペリフェラルのインスタンスは1つだけしかありません。しかし、どうすればそれをコードの構造として明確にできるでしょうか?

シングルトン

ソフトウェア工学において、シングルトン・パターンはクラスのインスタンス化を1つのオブジェクトに制限するデザインパターンです。

Wikipedia: Singleton Pattern

なぜグローバル変数は使えないのか?

このように、全てをパブリックかつスタティックにすることができます。

static mut THE_SERIAL_PORT: SerialPort = SerialPort; fn main() { let _ = unsafe { THE_SERIAL_PORT.read_speed(); } }

しかし、これにはいくつか問題があります。 これはミュータブルなグローバル変数であり、Rustにおいては、これらとやり取りするのは常にアンセーフです。 これらの変数はプログラムの全体を通して見えることになり、つまりそれは借用チェッカがこれらの変数の参照や所有権を追跡するのに役立たなくなることを意味します。

Rustではどうするか?

単にペリフェラルをグローバル変数にする代わりに、各ペリフェラル毎にOption<T>を含むPERIPHERALSと呼ばれるグローバル変数を作ることにします。

struct Peripherals {

serial: Option<SerialPort>,

}

impl Peripherals {

fn take_serial(&mut self) -> SerialPort {

let p = replace(&mut self.serial, None);

p.unwrap()

}

}

static mut PERIPHERALS: Peripherals = Peripherals {

serial: Some(SerialPort),

};

この構造体によって、ペリフェラルの唯一のインスタンスが取得できるようになります。

もしもtake_serial()を複数回呼び出そうとすれば、コードはパニックするでしょう。

fn main() { let serial_1 = unsafe { PERIPHERALS.take_serial() }; // This panics! // これはパニックします! // let serial_2 = unsafe { PERIPHERALS.take_serial() }; }

この構造体とのやり取りはunsafeにはなりますが、一度この構造体に含まれるSerialPortを取得してしまえばもうunsafeやPERIPHERALS構造体を使う必要は全くありません。

この方法では、オプション型の中にSerialPort構造体をラップし、take_serial()を一度コールする必要があるため、実行時に小さなオーバーヘッドとなります。

しかし、この少々のコストを前払いすることで、残りのプログラムで借用チェッカを利用できるようになるのです。

既存のライブラリによるサポート

上記のコードではPeripherals構造体を作りましたが、あなたのコードでも同じようにする必要はありません。

cortex_mクレートはこれと同様のことをしてくれるsingleton!()と呼ばれるマクロを含んでいます。

#[macro_use(singleton)] extern crate cortex_m; fn main() { // OK if `main` is executed only once, // `main`が一度だけしか実行されなければOKです let x: &'static mut bool = singleton!(: bool = false).unwrap(); }

加えて、あなたがcortex-m-rtfmクレートを使うのなら、これらのペリフェラルを定義・取得するプロセス全体は抽象化され、代わりにあなたが定義した全てのアイテムが、Option<T>なしで含まれているPeripherals構造体を手渡されます。

// cortex-m-rtfm v0.3.x

app! {

resources: {

static RX: Rx<USART1>;

static TX: Tx<USART1>;

}

}

fn init(p: init::Peripherals) -> init::LateResources {

// Note that this is now an owned value, not a reference

// これは所有された値であり、参照ではないことに注意してください

let usart1: USART1 = p.device.USART1;

}

しかしなぜ?

しかし、これらのシングルトンがRustのコードの動作にどのような顕著な違いをもたらすのでしょうか?

impl SerialPort {

const SER_PORT_SPEED_REG: *mut u32 = 0x4000_1000 as _;

fn read_speed(

&self // <------ This is really, really important

&self // <------ これは本当に、本当に重要です。

) -> u32 {

unsafe {

ptr::read_volatile(Self::SER_PORT_SPEED_REG)

}

}

}

ここには2つの重要な要素があります。

- シングルトンを使用しているため、

SerialPort構造体の取得手段や場所は1つだけになります。 read_speed()メソッドを呼ぶためには、SerialPort構造体の所有権もしくは参照を持つ必要があります。

これらの2つの要素をまとめると、借用チェッカを適切に満たしている場合のみハードウェアにアクセスできることを意味します。つまり、同じハードウェアに対して複数のミュータブルな参照を持つことはありません。

fn main() { // missing reference to `self`! Won't work. // `self`への参照が見つかりません。これはうまく動きません。 // SerialPort::read_speed(); let serial_1 = unsafe { PERIPHERALS.take_serial() }; // you can only read what you have access to // アクセスできるものだけ読み出すことができます。 let _ = serial_1.read_speed(); }

ハードウェアをデータのように扱う

加えて、いくつかの参照はミュータブルで、またいくつかはイミュータブルなため、関数またはメソッドがハードウェアの状態を変更できるかどうかを確認することが可能になります。

この関数はハードウェアの設定を変更できます。

fn setup_spi_port(

spi: &mut SpiPort,

cs_pin: &mut GpioPin

) -> Result<()> {

// ...

}

このメソッドは変更できません。

fn read_button(gpio: &GpioPin) -> bool {

// ...

}

これにより、実行時ではなくコンパイル時にコードがハードウェアを変更するかどうかを強制できます。 注意点としては、通常この強制はひとつのアプリケーション内でのみ機能します。ベアメタルシステムにおいては、ソフトウェアはひとつのアプリケーションにコンパイルされるため、これは一般的には制約にはなりません。

静的な保証

コンパイル時にデータ競合を防ぐのは、Rustの型システムです(SendとSyncトレイトを参照)。

この型システムは、コンパイル時に他のプロパティをチェックするためにも使用できます。

その結果、実行時チェックの必要性を減らせる場合があります。

組込みプログラムに適用する場合、これらの静的なチェックは、例えば、入出力インタフェースが正しく設定されていることを強制することができます。 例えば、使用されるピンを最初に設定することによってのみ、シリアルインタフェースを初期化できるようなAPI設計が可能です。

正しく設定されたペリフェラルでのみ、ピンをローレベルにするというような操作ができることを、 静的にチェックすることも可能です。例えば、フローティング入力モードに設定されたピンの出力状態を変更しようとすると、 コンパイルエラーが発生します。

訳注:フローティング入力モードは、ピンをハイインピーダンスの入力モードにしていることを意味しています。

以前の章で見た通り、所有権の概念はペリフェラルにも適用できます。所有権は、プログラムの特定部分のみがペリフェラルを変更することを保証します。 このアクセスコントロールは、ペリフェラルをグローバルでミュータブルな状態として扱う代替案と比較して、 ソフトウェアの解析をより簡単にします。

型状態プログラミング

型状態の概念は、オブジェクトの現在の状態に関する情報を、そのオブジェクトの型にエンコードすることを説明しています。 これは、少し難解に思えますが、Rustのビルダーパターンを使ったことがあるならば、既に型状態プログラミングを使い始めています。

#[derive(Debug)] struct Foo { inner: u32, } struct FooBuilder { a: u32, b: u32, } impl FooBuilder { pub fn new(starter: u32) -> Self { Self { a: starter, b: starter, } } pub fn double_a(self) -> Self { Self { a: self.a * 2, b: self.b, } } pub fn into_foo(self) -> Foo { Foo { inner: self.a + self.b, } } } fn main() { let x = FooBuilder::new(10) .double_a() .into_foo(); println!("{:#?}", x); }

この例では、Fooオブジェクトを直接作る方法はありません。必要なFooオブジェクトを取得する前に、FooBuilderを作り、正しく初期化しなければなりません。

この最小限の例は、2つの状態をエンコードしています。

FooBuilderは、「未設定」もしくは「設定中」の状態を表現します。Fooは、「設定済み」もしくは「使用準備完了」の状態を意味します。

強い型

Rustは強い型付けシステムを持っています。Fooのインスタンスを魔法のように作成したり、

into_foo()メソッドを呼び出すことなしにFooBuilderからFooに変換したりする、簡単な方法はありません。

さらに、into_foo()メソッドは、オリジナルのFooBuilder構造体を消費します。

これは、新しいインスタンスを作成しないと、再利用ができないことを意味します。

このことにより、システムの状態を型として表現することが可能になります。

そして、状態遷移に必要なアクションを、ある型と別の型とを交換するメソッドに取り入れることができます。

FooBuilderを作成し、Fooオブジェクトに交換することで、基本的なステートマシンのステップを見てきました。

ステートマシンとしてのペリフェラル

マイクロコントローラのペリフェラルは、一連のステートマシンとして考えることができます。 例えば、簡略化されたGPIOピンの設定は、次の状態ツリーとして表すことができます。

- 無効

- 有効

- 出力として設定

- 出力:ハイ

- 出力:ロー

- 入力として設定

- 入力:高抵抗(訳注:ハイインピーダンス)

- 入力:プルダウン

- 入力:プルアップ

- 出力として設定

このペリフェラルが無効モードから始まるとすると、入力:高抵抗モードに移行するには、次のステップを踏みます。

- 無効

- 有効

- 入力として設定

- 入力:高抵抗

入力:高抵抗から入力:プルダウンへと移る場合、次のステップを実行しなければなりません。

- 入力:高抵抗

- 入力:プルダウン

同じように、入力:プルダウンと設定されているGPIOピンを、出力:ハイにするには、次のステップを実行しなければなりません。

- 入力:プルダウン

- 入力として設定

- 出力として設定

- 出力:ハイ

ハードウェアの表現

通常、上記の状態は、GPIOペリフェラルに割り当てられたレジスタに値を書き込むことで設定できます。 これを説明するために、架空のGPIO設定レジスタを定義しましょう。

| 名前 | ビットフィールド | 値 | 意味 | 説明 |

|---|---|---|---|---|

| 有効 | 0 | 0 | 無効 | GPIOを無効にする |

| 1 | 有効 | GPIOを有効にする | ||

| 方向 | 1 | 0 | 入力 | 方向を入力に設定する |

| 1 | 出力 | 方向を出力に設定する | ||

| 入力モード | 2..3 | 00 | hi-z | 入力を高抵抗に設定する |

| 01 | プルダウン | 入力ピンはプルダウンになる | ||

| 10 | プルアップ | 入力ピンはプルアップになる | ||

| 11 | n/a | 無効な状態。設定しないこと。 | ||

| 出力モード | 4 | 0 | ロー | 出力ピンをローにする |

| 1 | ハイ | 出力ピンをハイにする | ||

| 入力状態 | 5 | x | 入力値 | 入力が1.5Vより低ければ0、1.5V以上であれば1 |

このGPIOを制御するために、次のようなRustの構造体を公開することが できます。

/// GPIO interface

/// GPIOインタフェース

struct GpioConfig {

/// GPIO Configuration structure generated by svd2rust

/// svd2rustで生成されたGPIO設定構造体

periph: GPIO_CONFIG,

}

impl Gpio {

pub fn set_enable(&mut self, is_enabled: bool) {

self.periph.modify(|_r, w| {

w.enable().set_bit(is_enabled)

});

}

pub fn set_direction(&mut self, is_output: bool) {

self.periph.modify(|r, w| {

w.direction().set_bit(is_output)

});

}

pub fn set_input_mode(&mut self, variant: InputMode) {

self.periph.modify(|_r, w| {

w.input_mode().variant(variant)

});

}

pub fn set_output_mode(&mut self, is_high: bool) {

self.periph.modify(|_r, w| {

w.output_mode.set_bit(is_high)

});

}

pub fn get_input_status(&self) -> bool {

self.periph.read().input_status().bit_is_set()

}

}

しかし、この実装では、筋が通らないレジスタの修正が可能になってしまいます。例えば、GPIOを入力に設定している時に、出力モードを設定すると、どうなるのでしょう?

通常、この構造体を利用すると、上のステートマシンで定義されていない状態に到達できてしまいます。 例えば、プルダウンの出力や、ハイに設定された入力、です。

このインタフェースは書き込みには便利ですが、ハードウェア実装によって定められた設計の契約を強制しません。

設計契約

前回、設計契約を強制しないインタフェースを書きました。架空のGPIO設定レジスタをもう一度見てみましょう。

| 名前 | ビットフィールド | 値 | 意味 | 説明 |

|---|---|---|---|---|

| 有効 | 0 | 0 | 無効 | GPIOを無効にする |

| 1 | 有効 | GPIOを有効にする | ||

| 方向 | 1 | 0 | 入力 | 方向を入力に設定する |

| 1 | 出力 | 方向を出力に設定する | ||

| 入力モード | 2..3 | 00 | hi-z | 入力を高抵抗に設定する |

| 01 | プルダウン | 入力ピンはプルダウンになる | ||

| 10 | プルアップ | 入力ピンはプルアップになる | ||

| 11 | n/a | 無効な状態。設定しないこと。 | ||

| 出力モード | 4 | 0 | ロー | 出力ピンをローにする |

| 1 | ハイ | 出力ピンをハイにする | ||

| 入力状態 | 5 | x | 入力値 | 入力が1.5Vより低ければ0、1.5V以上であれば1 |

ハードウェアを使う前に状態をチェックし、実行時に設計契約を強制すると、コードは次のように書くことができます。

/// GPIO interface

/// GPIOインタフェース

struct GpioConfig {

/// GPIO Configuration structure generated by svd2rust

/// svd2rustによって生成されたGPIO設定構造体

periph: GPIO_CONFIG,

}

impl Gpio {

pub fn set_enable(&mut self, is_enabled: bool) {

self.periph.modify(|_r, w| {

w.enable().set_bit(is_enabled)

});

}

pub fn set_direction(&mut self, is_output: bool) -> Result<(), ()> {

if self.periph.read().enable().bit_is_clear() {

// Must be enabled to set direction

// 方向を設定するには、有効化されてなければなりません

return Err(());

}

self.periph.modify(|r, w| {

w.direction().set_bit(is_output)

});

Ok(())

}

pub fn set_input_mode(&mut self, variant: InputMode) -> Result<(), ()> {

if self.periph.read().enable().bit_is_clear() {

// Must be enabled to set input mode

// 入力モードを設定するには、有効化されてなければなりません

return Err(());

}

if self.periph.read().direction().bit_is_set() {

// Direction must be input

// 方向は入力でなければなりません

return Err(());

}

self.periph.modify(|_r, w| {

w.input_mode().variant(variant)

});

Ok(())

}

pub fn set_output_status(&mut self, is_high: bool) -> Result<(), ()> {

if self.periph.read().enable().bit_is_clear() {

// Must be enabled to set output status

// 出力状態を設定するためには、有効化されてなければなりません

return Err(());

}

if self.periph.read().direction().bit_is_clear() {

// Direction must be output

// 方向は出力でなければなりません

return Err(());

}

self.periph.modify(|_r, w| {

w.output_mode.set_bit(is_high)

});

Ok(())

}

pub fn get_input_status(&self) -> Result<bool, ()> {

if self.periph.read().enable().bit_is_clear() {

// Must be enabled to get status

// 状態を取得するには、有効化されてなければなりません

return Err(());

}

if self.periph.read().direction().bit_is_set() {

// Direction must be input

// 方向は入力でなければなりません

return Err(());

}

Ok(self.periph.read().input_status().bit_is_set())

}

}

ハードウェアの制約を強制する必要があるため、時間とリソースを浪費する多くの実行時チェックを行うこととなり、開発者にとってこのコードは好ましくないです。

型状態

しかし、代わりに、状態遷移の規則を強制するために、Rustの型システムを使うとどうなるでしょうか?この例を見て下さい。

/// GPIO interface

/// GPIOインタフェース

struct GpioConfig<ENABLED, DIRECTION, MODE> {

/// GPIO Configuration structure generated by svd2rust

/// svd2rustによって生成されたGPIO設定構造体

periph: GPIO_CONFIG,

enabled: ENABLED,

direction: DIRECTION,

mode: MODE,

}

// Type states for MODE in GpioConfig

// GpioConfigのMODEのための型状態

struct Disabled;

struct Enabled;

struct Output;

struct Input;

struct PulledLow;

struct PulledHigh;

struct HighZ;

struct DontCare;

/// These functions may be used on any GPIO Pin

/// これらの関数はどのGPIOピンにも使えます

impl<EN, DIR, IN_MODE> GpioConfig<EN, DIR, IN_MODE> {

pub fn into_disabled(self) -> GpioConfig<Disabled, DontCare, DontCare> {

self.periph.modify(|_r, w| w.enable.disabled());

GpioConfig {

periph: self.periph,

enabled: Disabled,

direction: DontCare,

mode: DontCare,

}

}

pub fn into_enabled_input(self) -> GpioConfig<Enabled, Input, HighZ> {

self.periph.modify(|_r, w| {

w.enable.enabled()

.direction.input()

.input_mode.high_z()

});

GpioConfig {

periph: self.periph,

enabled: Enabled,

direction: Input,

mode: HighZ,

}

}

pub fn into_enabled_output(self) -> GpioConfig<Enabled, Output, DontCare> {

self.periph.modify(|_r, w| {

w.enable.enabled()

.direction.output()

.input_mode.set_high()

});

GpioConfig {

periph: self.periph,

enabled: Enabled,

direction: Output,

mode: DontCare,

}

}

}

/// This function may be used on an Output Pin

/// この関数はOutputピンに使用できます

impl GpioConfig<Enabled, Output, DontCare> {

pub fn set_bit(&mut self, set_high: bool) {

self.periph.modify(|_r, w| w.output_mode.set_bit(set_high));

}

}

/// These methods may be used on any enabled input GPIO

/// これらのメソッドは、有効化された入力GPIOに使えます

impl<IN_MODE> GpioConfig<Enabled, Input, IN_MODE> {

pub fn bit_is_set(&self) -> bool {

self.periph.read().input_status.bit_is_set()

}

pub fn into_input_high_z(self) -> GpioConfig<Enabled, Input, HighZ> {

self.periph.modify(|_r, w| w.input_mode().high_z());

GpioConfig {

periph: self.periph,

enabled: Enabled,

direction: Input,

mode: HighZ,

}

}

pub fn into_input_pull_down(self) -> GpioConfig<Enabled, Input, PulledLow> {

self.periph.modify(|_r, w| w.input_mode().pull_low());

GpioConfig {

periph: self.periph,

enabled: Enabled,

direction: Input,

mode: PulledLow,

}

}

pub fn into_input_pull_up(self) -> GpioConfig<Enabled, Input, PulledHigh> {

self.periph.modify(|_r, w| w.input_mode().pull_high());

GpioConfig {

periph: self.periph,

enabled: Enabled,

direction: Input,

mode: PulledHigh,

}

}

}

それでは、これを使うコードがどのようになるか、見てみましょう。

/*

* Example 1: Unconfigured to High-Z input

* 例1:未設定から高抵抗入力

*/

let pin: GpioConfig<Disabled, _, _> = get_gpio();

// Can't do this, pin isn't enabled!

// これはできません、ピンが有効になっていません!

// pin.into_input_pull_down();

// Now turn the pin from unconfigured to a high-z input

// 今度は、未設定から高抵抗入力に変えます

// 訳注:into_enabled_input()は入力モードを高抵抗にします

let input_pin = pin.into_enabled_input();

// Read from the pin

// ピンから値を読みます

let pin_state = input_pin.bit_is_set();

// Can't do this, input pins don't have this interface!

// これはできません、入力ピンはこのインタフェースを持っていません!

// input_pin.set_bit(true);

/*

* Example 2: High-Z input to Pulled Low input

* 例2:高抵抗入力からプルダウン入力

*/

let pulled_low = input_pin.into_input_pull_down();

let pin_state = pulled_low.bit_is_set();

/*

* Example 3: Pulled Low input to Output, set high

* 例3:プルダウン入力から出力、ハイを設定

*/

let output_pin = pulled_low.into_enabled_output();

output_pin.set_bit(false);

// Can't do this, output pins don't have this interface!

// これはできません、出力ピンはこのインタフェースを持っていません!

// output_pin.into_input_pull_down();

これは間違いなく、ピンの状態を保存するのに便利な方法ですが、なぜこのようにするのでしょうか?

なぜ、GpioConfig構造体の中で、状態をenumとして保存するより良い方法なのでしょうか?

コンパイル時の機能の安全性

コンパイル時に、設計契約を完全に強制しているため、実行時コストはかかりません。入力方向のピンに対して、出力モードを設定することは不可能です。 代わりに、そのピンを出力ピンに変換してから、出力モードを設定することで、状態を辿る必要があります。 このおかげで、関数実行前に現在の状態をチェックすることによる実行時ペナルティは、ありません。

型システムによってこれらの状態が強制されるため、このインタフェースの利用者によるエラーの余地はもはや残っていません。 もし利用者が不正な状態遷移をしようとすると、そのコードはコンパイルできません!

ゼロコスト抽象化

型状態はゼロコスト抽象化の優れた例でもあります。特定の動作を、コンパイル時の実行もしくは解析に移動する機能です。 これらの型状態は、実際のデータを含んでおらず、代わりにマーカとして使われています。 型状態はデータを含んでいないため、実行時、メモリ内に実際のデータはありません。

use core::mem::size_of;

let _ = size_of::<Enabled>(); // == 0

let _ = size_of::<Input>(); // == 0

let _ = size_of::<PulledHigh>(); // == 0

let _ = size_of::<GpioConfig<Enabled, Input, PulledHigh>>(); // == 0

ゼロサイズの型

struct Enabled;

上記のように定義された構造体をゼロサイズの型、と呼びます。これは、実際のデータを含んでいません。 これらの型は、コンパイル時には「実際に」機能します。例えば、コピーも、ムーブも、参照を取ることもできます。 しかし、最適化はこれらを完全に取り除きます。

次のコードスニペットを見てください。

pub fn into_input_high_z(self) -> GpioConfig<Enabled, Input, HighZ> {

self.periph.modify(|_r, w| w.input_mode().high_z());

GpioConfig {

periph: self.periph,

enabled: Enabled,

direction: Input,

mode: HighZ,

}

}

実行時、返り値のGpioConfigは、存在しません。この関数を呼び出すと、通常、1つのアセンブリ命令にまとめられます。

そのアセンブリ命令は、定数のレジスタ値を、レジスタの位置へ格納します。

これは、開発した型状態インタフェースが、ゼロコスト抽象化であることを意味します。

GpioConfigの状態を追跡するために、余分なCPU、RAM、コード領域を使用せず、直接レジスタアクセスするのと同じ機械語を表します。

ネスト

通常、これらの抽象化は、望み通りの深さでネストされます。使用される全てのコンポーネントが、ゼロサイズの型である限り、実行時には、構造体全体が存在しません。

複雑な構造体や深くネストした構造体については、全ての取り得る状態の組み合わせを定義することは、面倒です。 このような場合、全ての実装を生成するために、マクロが利用できます。

移植性

組込み環境においては、移植性は非常に重要なトピックです。1つのメーカから、それぞれのベンダや各プロダクトファミリが、異なるペリフェラルや機能を提供します、 異なるペリフェラルでは、ペリフェラルとやり取りする方法も異なります。

このような違いを吸収する一般的な方法は、ハードウェア抽象化レイヤまたはHALと呼ばれるレイヤを導入することです。

ハードウェア抽象化は、プラットフォーム固有の細部をエミュレーションして、プログラムにハードウェアリソースへ直接アクセスする方法を提供する、ソフトウェアの一連のルーチンです。

それらのルーチンがハードウェアへのオペレーティングシステム(OS)コールを提供することで、プログラマは、デイバスに依存せず、高性能なアプリケーションを書くことができます。

Wikipedia: ハードウェア抽象化レイヤ

組込みシステムは、通常オペレーティングシステムを使わず、ユーザがインストールできるソフトウェアもありません。 全体として1つにコンパイルされたファームウェアイメージであり、様々な制約を持つ、という点が特殊です。 そのため、Wikipediaで定義されている従来のアプローチでもうまく機能する可能性はありますが、移植性を確保するための最も有効なアプローチではない可能性があります。

Rustではどうするのでしょうか?embedded-halを見ていきましょう。

embedded-halとは?

一言で言えば、HAL実装、ドライバ、アプリケーションまたはファームウェア間の実装規約を定義するトレイトの集まりのことです。 それらの規約は、機能(ある型にトレイトが実装されていれば、HAL実装はそのトレイトの機能を提供します)とメソッド(あるトレイトを実装している型のオブジェクトを作成できれば、そのトレイトに含まれるメソッドが利用可能であることが保証されます)を含んでいます。

典型的なレイヤ構造は、次のようになります。

embedded-halで定義されているいくつかのトレイトを示します。

- GPIO(入出力ピン)

- シリアル通信

- I2C

- SPI

- タイマ/カウントダウン

- アナログデジタル変換

embedded-halトレイトと、それらを実装して使用するクレートを持つ主な理由は、複雑さを抑えることです。 アプリケーションがハードウェアのペリフェラルを使うコードだけでなく、追加するハードウェアコンポーネントのドライバを実装しなければならない場合を考えると、再利用性は非常に制限されます。 数学的に表現すると、MがペリフェラルHAL実装の数で、Nがドライバの数とするならば、全てのアプリケーションで車輪の再発明を行うことになります。 その結果、M*Nの実装が必要になります。 一方、embedded-halトレイトで提供されるAPIを使うことで、実装の複雑さはM+Nになるでしょう。 もちろん、明確に定義されたすぐに利用可能なAPIによって試行錯誤を減らすなど、他にも利点があります。

embedded-halのユーザ

上記のように、HALには主に3つのユーザがいます。

HAL実装

HAL実装は、ハードウェアとHALトレイトのユーザとの間のインタフェースを実装します。典型的な実装では、3つの部分から構成されます。

- 1つ以上のハードウェア固有の型

- そのような型のオブジェクトを作成し、初期化する関数。多くの場合、様々な設定オプションを提供しています(速度、動作モード、使用ピンなど)

- 1つ以上のその型に対するembedded-halの

traitimpl

このようなHAL実装は、様々な種類があります。

- 低レベルのハードウェアアクセスによるもの、例えばレジスタ

- オペレーティングシステムによるもの、例えばLinuxの

sysfsの使用 - アダプタによるもの、例えばユニットテストのための型のモック

- ハードウェアアダプタ用のドライバによるもの、例えばI2CマルチプレクサやGPIOエキスパンダ

ドライバ

ドライバは、embedded-halトレイトを実装しているペリフェラルに接続されている、内部または外部コンポーネントに対するカスタム機能を実装します。 そのようなドライバの典型的な例は、様々なセンサ(温度、磁気、加速度、輝度)、ディスプレイデバイス(LEDアレイ、LCDディスプレイ)や、アクチュエータ(モータ、トランスミッタ)を含みます。

ドライバは、embedded-halの特定のトレイトを実装する型のインスタンスと共に初期化する必要があります。 そのトレイトは、トレイト境界により保証され、駆動するデバイスとやり取りできるインスタンスをカスタムメソッドと共に提供します。

アプリケーション

アプリケーションは、様々な部品を結合し、必要な機能が確実に実現できるようにします。 別システムに移植する際、アプリケーションは最も適合作業が求められる部分です。アプリケーションは、HAL実装を通じて、実際のハードウェアを初期化する必要があるからです。 異なるハードウェアの初期化は、極端に異なる場合があります。 ユーザの選択は、多くの場合、大きな影響があります。 コンポーネントが別の端子に物理的に接続されたり、ハードウェアバスが機器構成を満たすために外部ハードウェアを必要とする場合があったり、内部ペリフェラルを使えるようにするための異なるトレードオフがあったりします。例えば、異なる機能を持つ複数のタイマが利用可能であること、や、ペリフェラルが他のペリフェラルと競合すること、です。

並行性

プログラムの異なる部分が様々なタイミングで実行されたり、アウトオブオーダに実行されると、並行性が発生します。 組込みでは、次のものが該当します。

- 割り込みが発生するたびに実行される割り込みハンドラ

- マイクロプロセッサがプログラムの一部を定期的にスワップする様々な形式のマルチスレッド

- システムによっては、各コアがプログラムの異なる部分を同時に独立して実行できるマルチコアマイクロプロセッサ